A Course Material on

# LINEAR INTEGRATED CIRCUITS AND APPLICATIONS

By

#### Mr.U.INIYAN

#### ASSISTANT PROFESSOR

#### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

PRATHYUSHA ENGINEERING COLLEGE

## EE8451 LINEAR INTEGRATED CIRCUITS AND APPLICATIONS LTP

## **OBJECTIVES:**

To study the IC fabrication procedure.

To study characteristics; realize circuits; design for signal analysis using Op-amp ICs. To study the applications of Op-amp.

To study internal functional blocks and the applications of special ICs like Timers, PLL circuits, regulator Circuits, ADCs.

## **UNIT I IC FABRICATION 9**

IC classification, fundamental of monolithic IC technology, epitaxial growth, masking and etching,

diffusion of impurities. Realisation of monolithic ICs and packaging. Fabrication of diodes, capacitance, resistance and FETs.

## **UNIT II CHARACTERISTICS OF OPAMP 9**

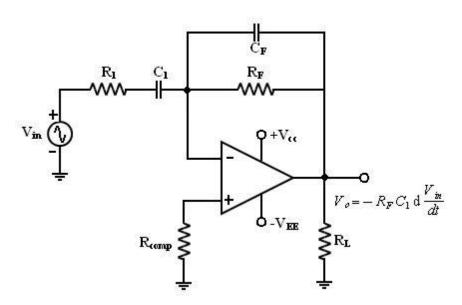

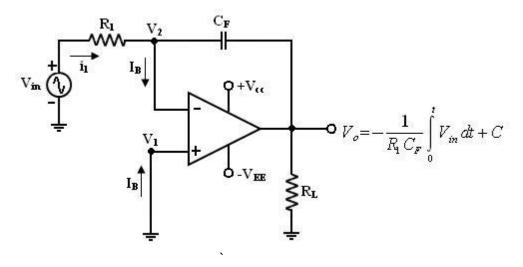

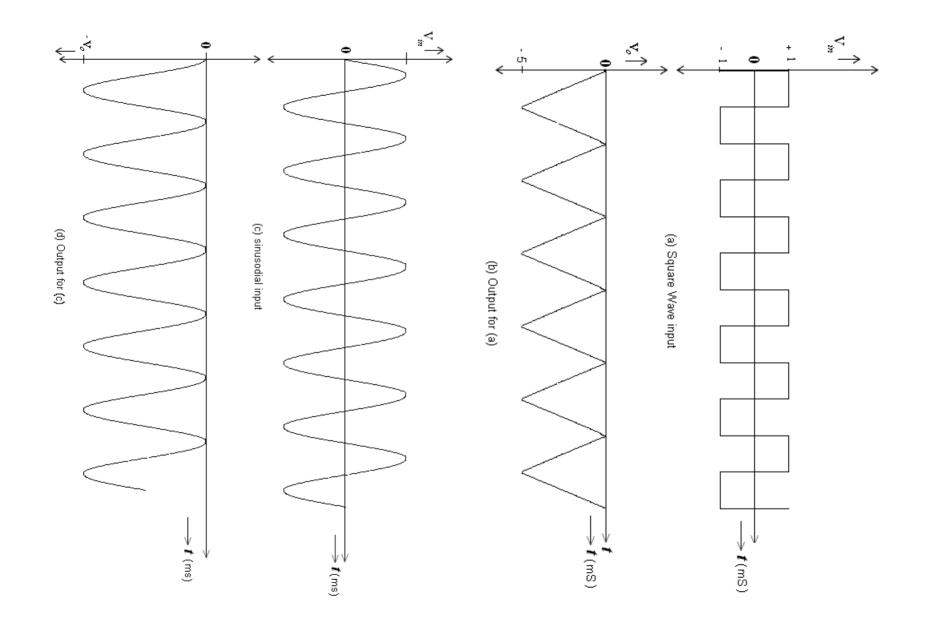

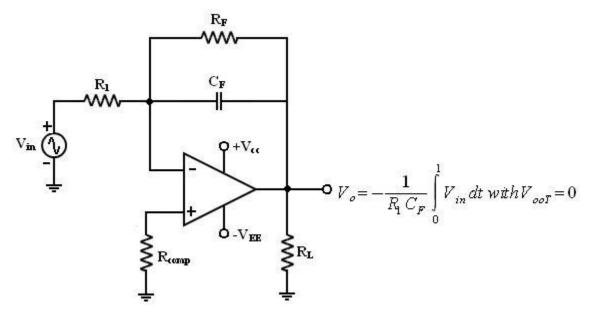

Ideal OP-AMP characteristics, DC characteristics, AC characteristics, differential amplifier; frequency response of OP-AMP; Basic applications of op-amp – Inverting and Non-inverting Amplifiers-V/I & I/V converters ,summer, differentiator and integrator.

## **UNIT III APPLICATIONS OF OPAMP 9**

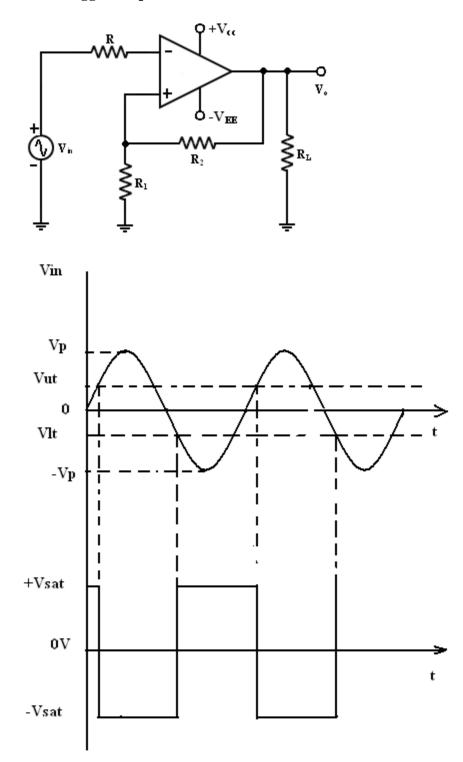

Instrumentation amplifier, Log and Antilog Amplifiers, first and second order active filters, , comparators, multivibrators, waveform generators, clippers, clampers, peak detector, S/H circuit, D/A

converter (R- 2R ladder and weighted resistor types), A/D converters using opamps.

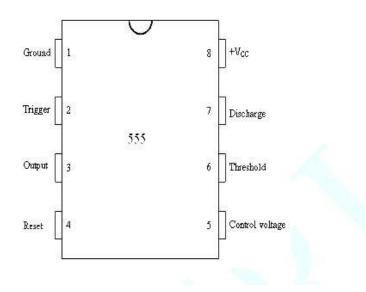

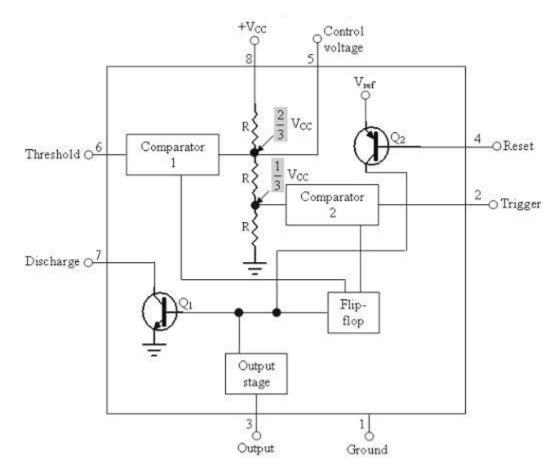

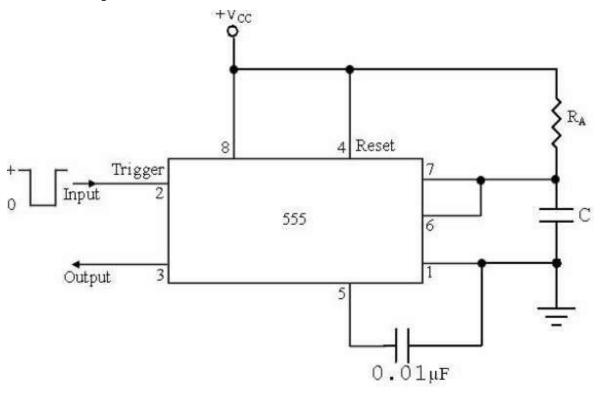

## **UNIT IV SPECIAL ICs 9**

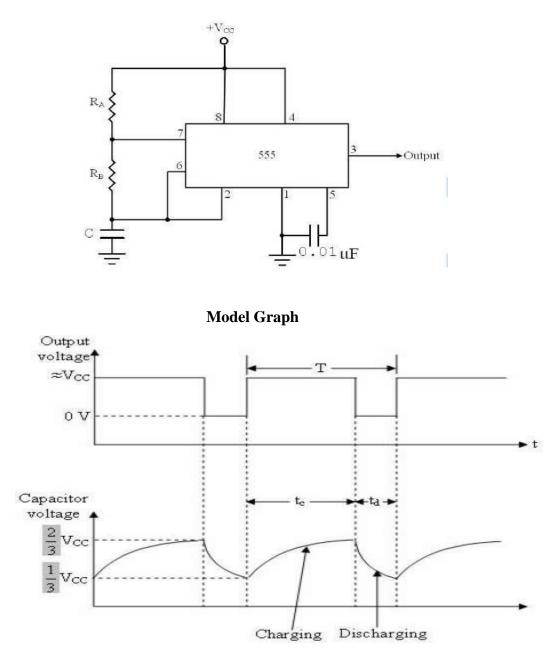

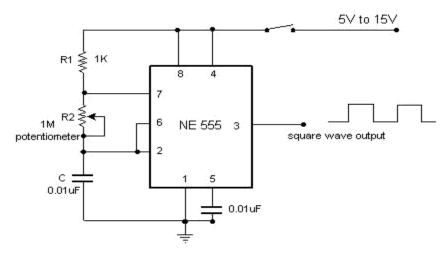

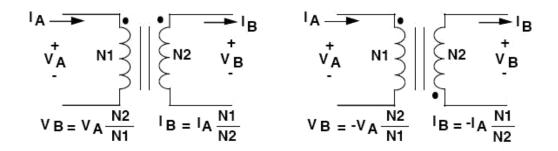

Functional block, characteristics & application circuits with 555 Timer Ic-566 voltage controlled

oscillator Ic; 565-phase lock loop Ic ,Analog multiplier ICs.

## UNIT V APPLICATION ICs 9

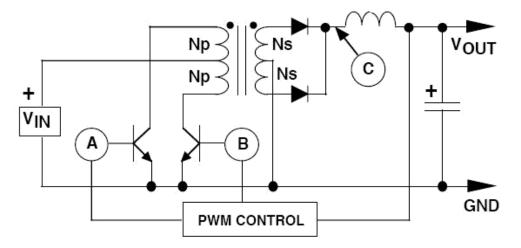

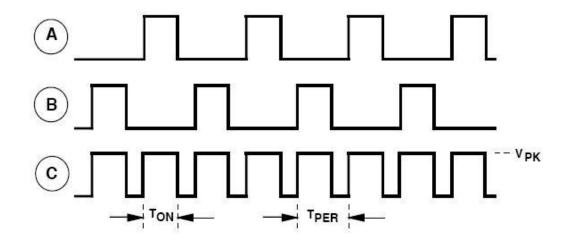

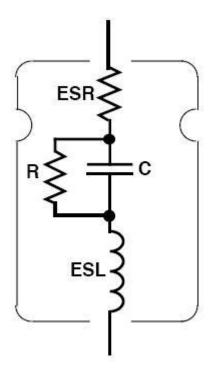

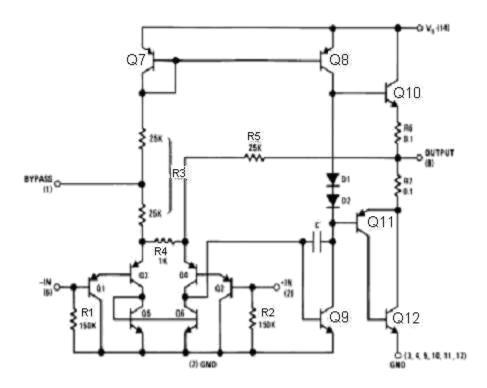

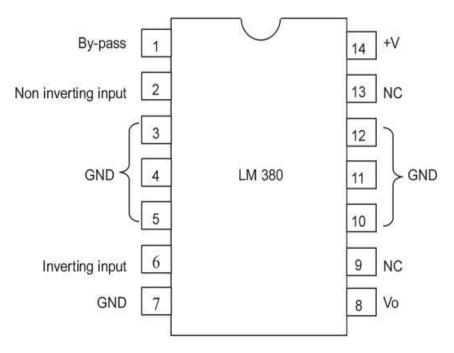

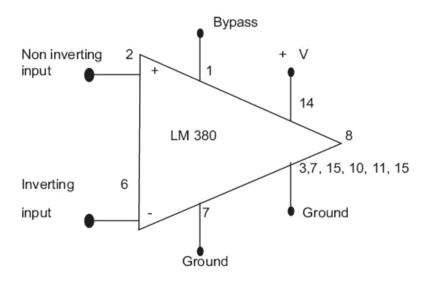

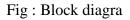

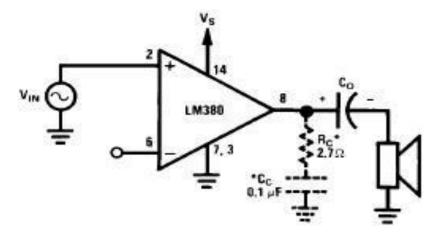

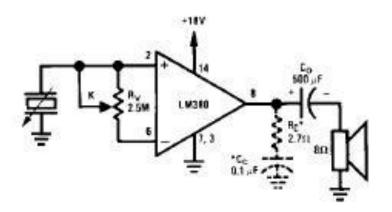

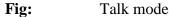

IC voltage regulators – LM78XX,79XX Fixed voltage regulators - LM317, 723 Variable voltage

regulators, switching regulator- SMPS- LM 380 power amplifier- ICL 8038 function generator IC.

# TOTAL: 45 PERIODS

## TEXT BOOKS:

1. David A.Bell, 'Op-amp & Linear ICs', Oxford, 2013.

2. D.Roy Choudhary, Sheil B.Jani, 'Linear Integrated Circuits', Il edition, New Age, 2003.

3. Ramakant A.Gayakward, 'Op-amps and Linear Integrated Circuits', IV edition, Pearson Education, 2003 / PHI. 2000.

## **REFERENCES:**

1. Fiore,"Opamps & Linear Integrated Circuits Concepts & Applications", Cengage, 2010.

2. Floyd ,Buchla,"Fundamentals of Analog Circuits, Pearson, 2013.

3. Jacob Millman, Christos C.Halkias, 'Integrated Electronics - Analog and Digital circuits system', Tata McGraw Hill, 2003

| S.NO       | ΤΟΡΙϹ                                           | PAGE NO. |  |

|------------|-------------------------------------------------|----------|--|

| UNIT I IO  | <b>C FABRICATION</b>                            | 5        |  |

| 1.1        | IC FABRICATION AND CIRCUIT CONFIGURATION        | 8        |  |

| 1.2        | Classification of ICs                           | 9        |  |

| 1.3        | Construction of a Monolithic Bipolar Transistor | 10       |  |

| 1.4        | Epitaxial growth                                | 12       |  |

| 1.5        | Masking and etching                             | 16       |  |

| 1.6        | Monolithic Ic packing                           | 17       |  |

| 1.7        | Fabrication of diodes                           | 18       |  |

| 1.8        | Fabrication of resistance and capacitance       | 25       |  |

| 1.9        | Fabrication of FETS                             | 30       |  |

| UNIT II C  | HARACTERISTICS OF OP-AMP                        |          |  |

| 2.1        | Op-Amp characteristics                          | 35       |  |

| 2.2        | AC- characteristics and DC characteristics      | 38       |  |

| 2.3        | Differential amplifiers                         | 46       |  |

| 2.4        | Frequency response of op- amp                   | 50       |  |

| 2.5        | Inverting and non-inverting amplifiers          | 59       |  |

| 2.6        | V/I,I/V Converters                              | 60       |  |

| 2.7        | Differentiator and integrator                   | 61       |  |

| UNIT III A | 62                                              |          |  |

| 3.1        | Instrumentation amplifiers                      | 72       |  |

| 3.2        | First, second order filters                     | 75       |  |

| 3.3        | Multivibrators                                  | 80       |  |

| 3.4        | Peak detector                                   | 95       |  |

| 3.5        | S/H Circuit                                     | 98       |  |

| 3.6        | A/DConverters                                   | 101      |  |

| UNIT IV S  | 109                                             |          |  |

| 4.1        | Functional block                                | 112      |  |

| 4.2        | Applications and circuit                        | 115      |  |

| 4.3        | 555 timer ics                                   | 119      |  |

| 4.4        | Ic 566 voltage controlled regulators            | 120      |  |

| 4.5        | 565 phase lock loop                             | 125      |  |

| 4.6        | Antilog multiplier                              | 130      |  |

| UNIT V     | APPLICATION OF ICS                              | 131      |  |

| 5.1        | Ic voltage regulator                            | 132      |  |

| 5.2        | LM 7812 Fixed Voltage Regulators                | 134      |  |

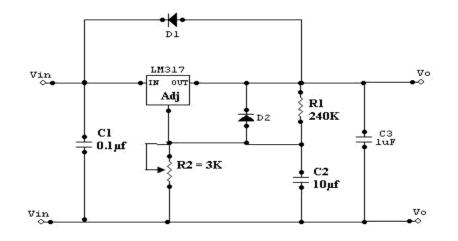

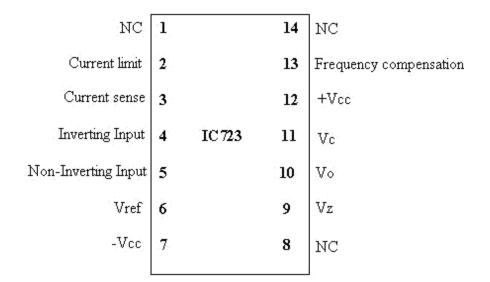

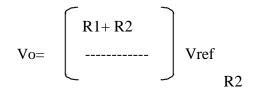

| 5.3        | LM 317 Regulator                                | 139      |  |

| 5.4        | Switching regulator                             | 140      |  |

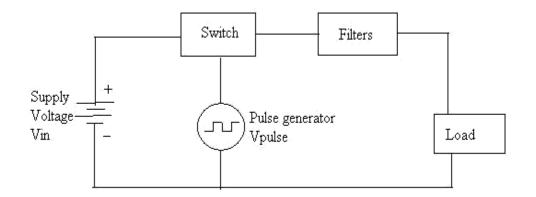

| 5.5        | SMPS Power Amplifiers                           | 148      |  |

# CONTENTS

## 1.1 IC FABRICATION AND CIRCUIT CONFIGURATION FOR LINEAR ICs

#### **1.1.1 Integrated Circuits**

An integrated circuit (IC) is a miniature, low cost electronic circuit consisting of active and passive components fabricated together on a single crystal of silicon. The active components are transistors and diodes and passive components are resistors and capacitors.

#### 1.1.2 .Advantages of integrated circuits:

Miniaturization and hence increased equipment density. Cost reduction due to batch processing. Increased system reliability due to the elimination of soldered joints. Improved functional performance. Matched devices. Increased operating speeds.

Reduction in power consumption

## **1.1.3 Classification:**

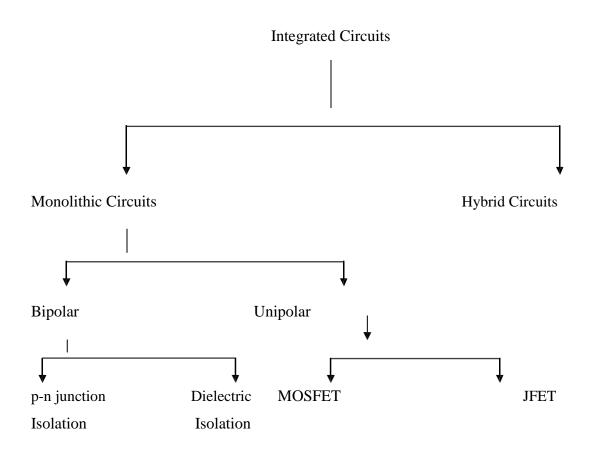

Integrated circuits can be classified into <u>analog</u>, <u>digital and mixed signal (both analog</u> and digital on the same chip). Based upon above requirement two different IC technology namely Monolithic Technology and Hybrid Technology have been developed. In monolithic IC ,all circuit components ,both active and passive elements and their interconnections are manufactured into or on top of a single chip of silicon. In hybrid circuits, separate component parts are attached to a ceramic substrate and interconnected by means of either metallization pattern or wire bounds.

Digital integrated circuits can contain anything from one to millions of <u>logic gates</u>, <u>flip-flops</u>, <u>multiplexers</u>, and other circuits in a few square millimeters. The small size of these circuits allows high speed, low power dissipation, and reduced manufacturing cost compared with board-level

integration. These digital ICs, typically <u>microprocessors, DSPs</u>, and micro controllers work using binary mathematics to process "one" and "zero" signals.

Analog ICs, such as sensors, power management circuits, and <u>operational amplifiers</u>, work by processing continuous signals. They perform functions like <u>amplification</u>, active filtering, <u>demodulation</u>, <u>mixing</u>, etc. Analog ICs ease the burden on circuit designers by having expertly designed analog circuits available instead of designing a difficult analog circuit from scratch.

ICs can also combine analog and digital circuits on a single chip to create functions such as  $\underline{A/D}$  converters and  $\underline{D/A}$  converters. Such circuits offer smaller size and lower cost, but must carefully account for signal interference

## **1.2 Classification of ICs:**

#### Generations

#### 1.1.5 SSI, MSI and LSI

The first integrated circuits contained only a few transistors. Called "Small-Scale Integration" (SSI), digital circuits containing transistors numbering in the tens provided a few logic gates for example, while early linear ICs such as the <u>Plessey SL201</u> or the <u>Philips TAA320</u> had as few as two transistors. The term Large Scale Integration was first used by IBM scientist Rolf Landauer when describing the theoretical concept, from there came the terms for SSI, MSI, VLSI, and ULSI. They began to appear in consumer products at the turn of the decade, a typical application being <u>FM</u> inter-carrier sound processing in <u>television</u> receivers.

The next step in the development of integrated circuits, taken in the late 1960s, introduced devices which contained hundreds of transistors on each chip, called "Medium-Scale Integration" (MSI). They were attractive economically because while they cost little more to produce than SSI devices, they allowed more complex systems to be produced using smaller circuit boards, less assembly work (because of fewer separate components), and a number of other advantages.

#### 1.1.6 VLSI

The final step in the development process, starting in the 1980s and continuing through the present, was "very large-scale integration" (VLSI). The development started with hundreds of thousands of transistors in the early 1980s, and continues beyond several billion transistors as of 2007. In 1986 the first one megabit <u>RAM chips</u> were introduced, which contained more than one million transistors. Microprocessor chips passed the million transistor mark in 1989 and the billion transistor mark in 2005

#### 1.1.7 ULSI, WSI, SOC and 3D-IC

To reflect further growth of the complexity, the term ULSI that stands for "Ultra-Large Scale Integration" was proposed for chips of complexity of more than 1 million transistors.

<u>Wafer-scale integration (W</u>SI) is a system of building very-large integrated circuits that uses an entire silicon wafer to produce a single "super-chip". Through a combination of large size and reduced packaging, WSI could lead to dramatically reduced costs for some systems, notably

massively parallel supercomputers. The name is taken from the term Very-Large-Scale Integration, the current state of the art when WSI was being developed.

<u>System-on-a-Chip (SoC</u> or SOC) is an integrated circuit in which all the components needed for a computer or other system are included on a single chip. The design of such a device can be complex and costly, and building disparate components on a single piece of silicon may compromise the efficiency of some elements.

However, these drawbacks are offset by lower manufacturing and assembly costs and by a greatly reduced power budget: because signals among the components are kept on-die, much less power is require. <u>Three Dimensional Integrated Circuit (3D-IC)</u> has two or more layers of active electronic components that are integrated both vertically and horizontally into a single circuit. Communication between layers uses on-die signaling, so power consumption is much lower than in equivalent separate circuits. Judicious use of short vertical wires can substantially reduce overall wire length for faster operation.

## **1.3** Construction of a Monolithic Bipolar Transistor:

The fabrication of a monolithic transistor includes the following steps.

- 1. Epitaxial growth

- 2. Oxidation

- 3. Photolithography

- 4. Isolation diffusion

- 5. Base diffusion

- 6. Emitter diffusion

- 7. Contact mask

- 8. Aluminium metallization

- 9. Passivation

The letters P and N in the figures refer to type of doping, and a minus (-) or plus (+) with P and N indicates lighter or heavier doping respectively.

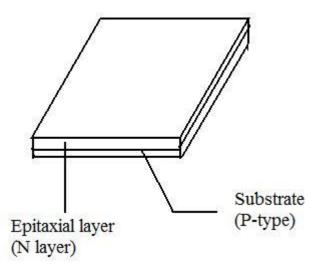

## 1. Epitaxial growth:

The first step in transistor fabrication is creation of the collector region. We normally require a low resistivity path for the collector current. This is due to the fact that, the collector contact is normally taken at the top, thus increasing the collector series resistance and the  $V_{CE(Sat)}$  of the device.

The higher collector resistance is reduced by a process called buried layer as shown in figure. In this arrangement, a heavily doped \_N' region is sandwiched between the N-type epitaxial layer and P – type substrate. This buried N<sup>+</sup> layer provides a low resistance path in the active collector

region to the collector contact C. In effect, the buried layer provides a low resistance shunt path for the flow of current.

For fabricating an NPN transistor, we begin with a P-type silicon substrate having a resistivity of typically 1 $\Omega$ -cm, corresponding to an acceptor ion concentration of 1.4 \* 10<sup>15</sup> atoms/cm<sup>3</sup>. An oxide mask with the necessary pattern for buried layer diffusion is prepared. This is followed by masking and etching the oxide in the buried layer mask.

The N-type buried layer is now diffused into the substrate. A slow-diffusing material such as arsenic or antimony us used, so that the buried layer will stay-put during subsequent diffusions. The junction depth is typically a few microns, with sheet resistivity of around  $20\Omega$  per square.

Then, an epitaxial layer of lightly doped N-silicon is grown on the P-type substrate by placing the wafer in the furnace at  $1200^{0}$  C and introducing a gas containing phosphorus (donor impurity). The resulting structure is shown in figure.

The subsequent diffusions are done in this epitaxial layer. All active and passive components are formed on the thin N-layer epitaxial layer grown over the P-type substrate. Obtaining an epitaxial layer of the proper thickness and doping with high crystal quality is perhaps the most formidable challenge in bipolar device processing.

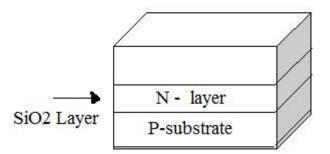

#### 2. Oxidation:

As shown in figure, a thin layer of silicon dioxide (SiO<sub>2</sub>) is grown over the N-type layer by exposing the silicon wafer to an oxygen atmosphere at about  $1000^{0}$  C.

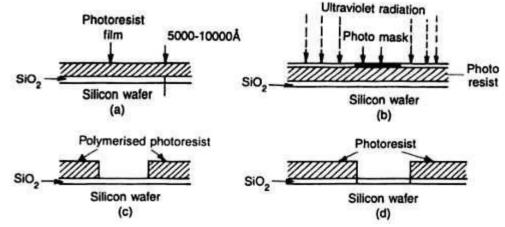

## 3. Photolithography:

The prime use of photolithography in IC manufacturing is to selectively etch or remove the SiO<sub>2</sub> layer. As shown in figure, the surface of the oxide is first covered with a thin uniform layer of photosensitive emulsion (Photo resist). The mask, a black and white negative of the requied pattern, is placed over the structure. When exposed to ultraviolet light, the photo resist under the transparent region of the mask becomes poly-merized. The mask is then removed and the wafer is treated chemically that removes the unexposed portions of the photoresist film. The polymerized region is cured so that it becomes resistant to corrosion. Then the chip is dipped in an etching solution of hydrofluoric acid which removes the oxide layer not protected by the polymerized photoresist. This creates openings in the SiO<sub>2</sub> layer through which P-type or N-type impurities can be diffused using the isolation diffusion process as shown in figure. After diffusion of impurities, the polymerized photoresist is removed with sulphuric acid and by a mechanical abrasion process.

#### 4. Isolation Diffusion:

The integrated circuit contains many devices. Since a number of devices are to be fabricated on the same IC chip, it becomes necessary to provide good isolation between various components and their interconnections.

The most important techniques for isolation are:

- 1. PN junction Isolation

- 2. Dielectric Isolation

In PN junction isolation technique, the  $P^+$  type impurities are selectively diffused into the N-type epitaxial layer so that it touches the P-type substrate at the bottom. This method generated N-type isolation regions surrounded by P-type moats. If the P-substrate is held at the most negative potential, the diodes will become reverse-biased, thus providing isolation between these islands.

The individual components are fabricated inside these islands. This method is very economical, and is the most commonly used isolation method for general purpose integrated circuits. In dielectric isolation method, a layer of solid dielectric such as silicon dioxide or ruby surrounds each component and this dielectric provides isolation. The isolation is both physical and electrical. This method is very expensive due to additional processing steps needed and this is mostly used for fabricating IC's required for special application in military and aerospace.

The PN junction isolation diffusion method is shown in figure. The process take place in a furnace using boron source. The diffusion depth must be atleast equal to the epitaxial thickness in order to obtain complete isolation. Poor isolation results in device failures as all transistors might get shorted together. The N-type island shown in figure forms the collector region of the NPN transistor. The heavily doped P-type regions marked  $P^+$  are the isolation regions for the active and passive components that will be formed in the various N-type islands of the epitaxial layer.

## **5** Base diffusion:

Formation of the base is a critical step in the construction of a bipolar transistor. The base must be aligned, so that, during diffusion, it does not come into contact with either the isolation region or the buried layer. Frequently, the base diffusion step is also used in parallel to fabricate diffused resistors for the circuit. The value of these resistors depends on the diffusion conditions and the width of the opening made during etching. The base width influences the transistor parameters very strongly. Therefore, the base junction depth and resistivity must be tightly controlled. The base sheet resistivity should be fairly high (200-  $500\Omega$  per square) so that the base does not inject carriers into the emitter. For NPN transistor, the base is diffused in a furnace using a boron source. The diffusion process is done in two steps, pre deposition of dopants at  $900^0$  C and driving them in at about  $1200^0$  C. The drive-in is done in an oxidizing ambience, so that oxide is grown over the base region for subsequent fabrication steps. Figure shows that P-type base region of the transistor diffusion diffusion processes.

#### 6. Emitter Diffusion:

Emitter Diffusion is the final step in the fabrication of the transistor. The emitter opening must lie wholly within the base. Emitter masking not only opens windows for the emitter, but also for the contact point, which provides a low resistivity ohmic contact path for the emitter terminal.

The emitter diffusion is normally a heavy N-type diffusion, producing low-resistivity layer that can inject charge easily into the base. A Phosphorus source is commonly used so that the diffusion time id shortened and the previous layers do not diffuse further. The emitter is diffused into the base, so that the emitter junction depth very closely approaches the base junction depth. The active base is then a P-region between these two junctions which can be made very narrow by adjusting the emitter diffusion time. Various diffusion and drive in cycles can be used to fabricate the emitter. The Resistivity of the emitter is usually not too critical.

The N-type emitter region of the transistor diffused into the P-type base region is shown below. However, this is not needed to fabricate a resistor where the resistivity of the P-type base region itself will serve the purpose. In this way, an NPN transistor and a resistor are fabricated simultaneously.

#### 7. Contact Mask:

After the fabrication of emitter, windows are etched into the N-type regions where contacts are to be made for collector and emitter terminals. Heavily concentrated phosphorus  $N^+$  dopant is diffused into these regions simultaneously.

The reasons for the use of heavy  $N^+$  diffusion is explained as follows: Aluminium, being a good conductor used for interconnection, is a P-type of impurity when used with silicon. Therefore, it can produce an unwanted diode or rectifying contact with the lightly doped N-material. Introducing a high concentration of  $N^+$  dopant caused the Si lattice at the surface semi-metallic. Thus the  $N^+$  layer makes a very good ohmic contact with the Aluminium layer. This is done by the oxidation, photolithography and isolation diffusion processes.

#### 8. Metallization:

The IC chip is now complete with the active and passive devices, and the metal leads are to be formed for making connections with the terminals of the devices. Aluminium is deposited over the entire wafer by vacuum deposition. The thickness for single layer metal is  $1\mu$  m. Metallization is carried out by evaporating aluminium over the entire surface and then selectively etching away aluminium to leave behind the desired interconnection and bonding pads as shown in figure.

Metallization is done for making interconnection between the various components fabricated in an IC and providing bonding pads around the circumference of the IC chip for later connection of wires

#### 9. Passivation/ Assembly and Packaging:

Metallization is followed by passivation, in which an insulating and protective layer is deposited over the whole device. This protects it against mechanical and chemical damage during subsequent processing steps. Doped or undoped silicon oxide or silicon nitride, or some combination of them, are usually chosen for passivation of layers. The layer is deposited by chemical vapour deposition (CVD) technique at a temperature low enough not to harm the metallization.

#### **1.4 Transistor Fabrication:**

#### **PNP** Transistor:

.

The integrated PNP transistors are fabricated in one of the following three structures.

- 1. Substrate or Vertical PNP

- 2. Lateral or horizontal PNP and

- 3. Triple diffused PNP

#### Substrate or Vertical PNP:

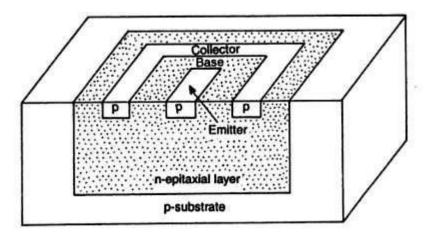

The P-substrate of the IC is used as the collector, the N-epitaxial layer is used as the base and the next P-diffusion is used as the emitter region of the PNP transistor. The structure of a vertical monolithic PNP transistor  $Q_1$  is shown in figure. The base region of an NPN transistor structure is formed in parallel with the emitter region of the PNP transistor.

The method of fabrication has the disadvantage of having its collector held at a fixed negative potential. This is due to the fact that the P-substrate of the IC is always held at a negative potential normally for providing good isolation between the circuit components and the substrate. <u>Triple diffused PNP:</u>

This type of PNP transistor is formed by including an additional diffusion process over the standard NPN transistor processing steps. This is called a triple diffusion process, because it involves an additional diffusion of P-region in the second N-diffusion region of a NPN transistor. The structure of the triple diffused monolithic PNP transistor Q<sub>2</sub> is also shown in the below figure.

This has the limitations of requiring additional fabrication steps and sophisticated fabrication assemblies.

# **1.1.10 Lateral or Horizontal PNP:**

This is the most commonly used form of integrated PNP transistor fabrication method. This has the advantage that it can be fabricated simultaneously with the processing steps of an NPN transistor and therefore it requires as the base of the PNP transistor. During the P-type base diffusion process of NPN transistor, two parallel P-regions are formed which make the emitter and collector regions of the horizontal PNP transistor.

Fig. 1.17 A pnp lateral transistor

Comparison of monolithic NPN and PNP transistor:

Normally, the NPN transistor is preferred in monolithic circuits due to the following reasons:

1. The vertical PNP transistor must have his collector held at a fixed negative voltage.

2. The lateral PNP transistor has very wide base region and has the limitation due to the lateral diffusion of P-type impurities into the N-type base region. This makes the photographic mask making, alignment and etching processes very difficult. This reduces the current gain of lateral PNP transistors as low as 1.5 to 30 as against 50 to 300 for a monolithic NPN transistor.

3. The collector region is formed prior to the formation of base and emitter diffusion. During the later diffusion steps, the collector impurities diffuse on either side of the defined collector junction. Since the N-type impurities have smaller diffusion constant compared to P-type impurities the N-

type collector performs better than the P-type collector. This makes the NPN transistor preferable for monolithic fabrication due to the easier process control.

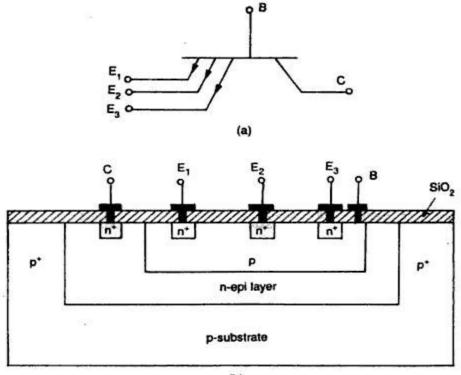

Transistor with multiple emitters: The applications such as transistor- transistor logic (TTL) require multiple emitters. The below figure shows the circuit sectional view of three N-emitter regions diffused in three places inside the P-type base. This arrangement saves the chip area and enhances the component density of the IC.

(b)

Fig. 1.18 (a) Multi-emitter transistor, (b) Cross-sectional view of a multi-emitter transistor

#### **<u>1.5 Schottky Barrier Diode:</u>**

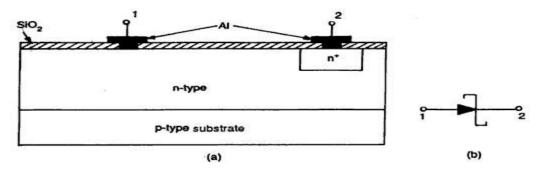

Fig. 1.21 (a) A Schottky diode, (b) Symbol for metal semiconductor diode

The metal contacts are required to be ohmic and no PN junctions to be formed between the metal and silicon layers. The  $N^+$  diffusion region serves the purpose of generating ohmic contacts. On the other hand, if aluminium is deposited directly on the N-type silicon, then a metal semiconductor diode can be said to be formed. Such a metal semiconductor diode junction exhibits the same type of V-I Characteristics as that of an ordinary PN junction.

The cross sectional view and symbol of a Schottky barrier diode as shown in figure. Contact 1 shown in figure is a Schottky barrier and the contact 2 is an ohmic contact. The contact potential between the semiconductor and the metal generated a barrier for the flow of conducting electrons from semiconductor to metal. When the junction is forward biased this barrier is lowered and the electron flow is allowed from semiconductor to metal, where the electrons are in large quantities.

The minority carriers carry the conduction current in the Schottky diode whereas in the PN junction diode, minority carriers carry the conduction current and it incurs an appreciable time delay from ON state to OFF state. This is due to the fact that the minority carriers stored in the junction have to be totally removed. This characteristic puts the Schottky barrier diode at an advantage since it exhibits negligible time to flow the electron from N-type silicon into aluminum almost right at the contact surface, where they mix with the free electrons. The other advantage of this diode is that it has less forward voltage (approximately 0.4V). Thus it can be used for clamping and detection in high frequency applications and microwave integrated circuits.

#### 1.1.12 Schottky transistor:

Fig. 1.19 (a) A transistor with a Schottky-barrier diode clamped between base and collector to prevent saturation, (b) Cross-section of a Schottky-barrier transistor, (c) Symbolic representation

The cross-sectional view of a transistor employing a Schottky barrier diode clamped between its base and collector regions is shown in figure. The equivalent circuit and the symbolic representation of the Schottky transistor are shown in figure. The Schottky diode is formed by allowing aluminium metallization for the base lead which makes contact with the N-type collector region also as shown in figure.

When the base current is increased to saturate the transistor, the voltage at the collector C reduces and this makes the diode Ds conduct. The base to collector voltage reduces to 0.4V, which is less the cut-in-voltage of a silicon base-collector junction. Therefore, the transistor does not get saturated.

## **1.6 Monolithic diodes:**

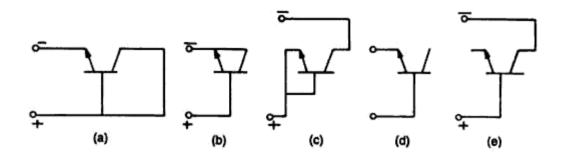

The diode used in integrated circuits are made using transistor structures in one of the five possible connections. The three most popular structures are shown in figure. The diode is obtained from a transistor structure using one of the following structures.

- 1. The emitter-base diode, with collector short circuited to the base.

- 2. The emitter-base diode with the collector open and

- 3. The collector –base diode, with the emitter open-circuited.

The choice of the diode structure depends on the performance and application desired. Collectorbase diodes have higher collector-base arrays breaking rating, and they are suitable for commoncathode diode arrays diffused within a single isolation island. The emitter-base diffusion is very popular for the fabrication of diodes, provided the reverse-voltage requirement of the circuit does not exceed the lower base-emitter breakdown voltage.

| Characteristic                | $V_{CB}^{(a)} = 0$ | (b)<br>V <sub>CE</sub> = 0<br>7 | (c)<br>V <sub>E0</sub> = 0<br>55 | (d)<br>I <sub>C</sub> = 0<br>7 | (e)<br>I <sub>E</sub> = 0<br>55 |

|-------------------------------|--------------------|---------------------------------|----------------------------------|--------------------------------|---------------------------------|

| Breakdown voltage<br>in volts |                    |                                 |                                  |                                |                                 |

| Storage time, n sec           | 9                  | 100                             | 53                               | 56                             | 85                              |

| Forward voltage<br>in volts   | .85                | .92                             | .94                              | .96                            | .95                             |

#### **1.1.14 Integrated Resistors:**

A resistor in a monolithic integrated circuit is obtained by utilizing the bulk resistivity of the diffused volume of semiconductor region. The commonly used methods for fabricating integrated resistors are 1. Diffused 2. epitaxial 3. Pinched and 4. Thin film techniques.

#### **1.1.15 Diffused Resistor:**

The diffused resistor is formed in any one of the isolated regions of epitaxial layer during base or emitter diffusion processes. This type of resistor fabrication is very economical as it runs in parallel to the bipolar transistor fabrication. The N-type emitter diffusion and P-type base diffusion are commonly used to realize the monolithic resistor.

The diffused resistor has a severe limitation in that, only small valued resistors can be fabricated. The surface geometry such as the length, width and the diffused impurity profile determine the resistance value. The commonly used parameter for defining this resistance is called the sheet resistance. It is defined as the resistance in ohms/square offered by the diffused area.

In the monolithic resistor, the resistance value is expressed by

$R = R_s 1/w$  where R = resistance offered (in ohms)

$R_s$  = sheet resistance of the particular fabrication process involved (in ohms/square)

l = length of the diffused area and w = width of the diffused area.

The sheet resistance of the base and emitter diffusion in 200 $\Omega$ /Square and 2.2 $\Omega$ /square respectively. For example, an emitter-diffused strip of 2mil wide and 20 mil long will offer a resistance of 22 $\Omega$ . For higher values of resistance, the diffusion region can be formed in a zig-zag fashion resulting in larger effective length. The poly silicon layer can also be used for resistor realization.

# **1.1.16 Epitaxial Resistor:**

# Fig. 1.23 (a) Epitaxial resistor

The N-epitaxial layer can be used for realizing large resistance values. The figure shows the crosssectional view of the epitaxial resistor formed in the epitaxial layer between the two  $N^+$  aluminium metal contacts.

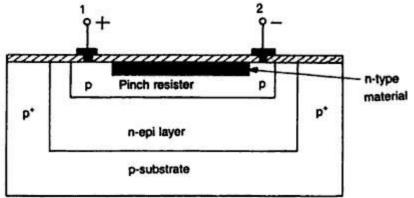

# 1.1.17 Pinched resistor:

# Fig. 1.23 (b) Cross-sectional view of a pinch resistor

The sheet resistance offered by the diffusion regions can be increased by narrowing down its cross-sectional area. This type of resistance is normally achieved in the base region. Figure shows a pinched base diffused resistor. It can offer resistance of the order of mega ohms in a comparatively smaller area. In the structure shown, no current can flow in the N-type material since the diode realized at contact 2 is biased in reversed direction. Only very small reverse saturation current can flow in conduction path for the current has been reduced or pinched. Therefore, the resistance between the contact 1 and 2 increases as the width narrows down and hence it acts as a pinched resistor.

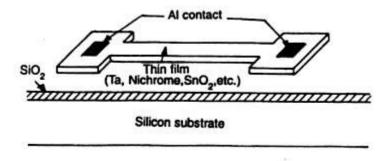

## **<u>1.1.18Thin film resistor:</u>**

Fig. 1.23 (c) Cross-section of a thin film resistor

The thin film deposition technique can also be used for the fabrication of monolithic resistors. A very thin metallic film of thickness less than 1µm is deposited on the silicon dioxide layer by vapour deposition techniques. Normally, Nichrome (NiCr) is used for this process. Desired geometry is achieved using masked etching processes to obtain suitable value of resistors. Ohmic contacts are made using aluminium metallization as discussed in earlier sections.

The cross-sectional view of a thin film resistor as shown in figure. Sheet resistances of 40 to 400 $\Omega$ / square can be easily obtained in this method and thus 20k $\Omega$  to 50k $\Omega$  values are very practical.

The advantages of thin film resistors are as follows:

- 1. They have smaller parasitic components which makes their high frequency behaviour good.

- 2. The thin film resistor values can be very minutely controlled using laser trimming.

- 3. They have low temperature coefficient of resistance and this makes them more stable.

The thin film resistor can be obtained by the use of tantalum deposited over silicon dioxide layer. The main disadvantage of thin film resistor is that its fabrication requires additional processing steps.

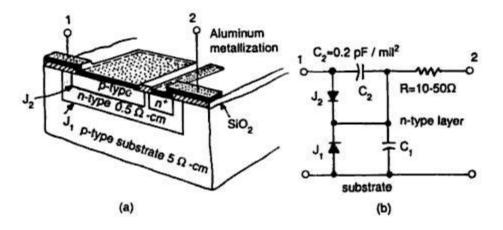

## **<u>1.7 Monolithic Capacitors</u>:**

Fig. 1.24 (a) Junction-type IC capacitor, (b) Equivalent circuit

Monolithic capacitors are not frequently used in integrated circuits since they are limited in the range of values obtained and their performance. There are, however, two types available, the junction capacitor is a reverse biased PN junction formed by the collector-base or emitter-base diffusion of the transistor. The capacitance is proportional to the area of the junction and inversely proportional to the depletion thickness.

- C  $\alpha$  A, where a is the area of the junction and

- $C \alpha T$ , where t is the thickness of the depletion layer.

The capacitance value thus obtainable can be around  $1.2nF/mm^2$ .

The thin film or metal oxide silicon capacitor uses a thin layer of silicon dioxide as the dielectric. One plate is the connecting metal and the other is a heavily doped layer of silicon, which is formed during the emitter diffusion. This capacitor has a lower leakage current and is non-directional, since emitter plate can be biased positively. The capacitance value of this method can be varied between 0.3 and  $0.8 \text{nF/mm}^2$ .

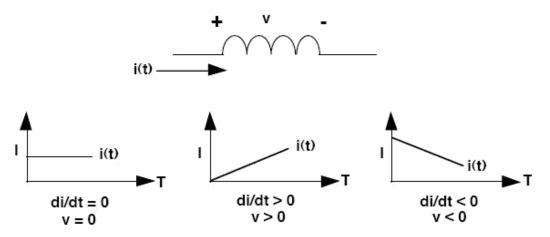

## 1.1.20 Inductors:

No satisfactory integrated inductors exist. If high Q inductors with inductance of values larger than  $5\mu$ H are required, they are usually supplied by a wound inductor which is connected externally to the chip. Therefore, the use of inductors is normally avoided when integrated circuits are used.

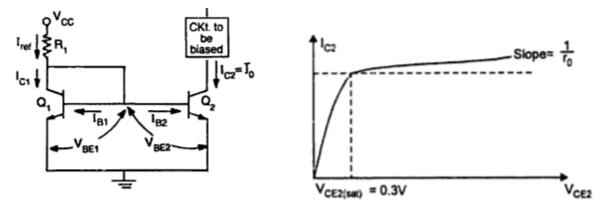

#### **1.8 CURRENT MIRROR AND CURRENT SOURCES:**

#### **Constant current source(Current Mirror):**

A constant current source makes use of the fact that for a transistor in the active mode of operation, the collector current is relatively independent of the collector voltage. In the basic circuit shown in fig 1

Transistors  $Q_1\&Q_2$  are matched as the circuit is fabricated using IC technology. Base and emitter of  $Q_1\&Q_2$  are tied together and thus have the same VBE. In addition, transistor Q1 is connected as a diode by shorting it s collector to base. The input current Iref flows through the diode connected transistor Q1 and thus establishes a voltage across Q1.

This voltage in turn appears between the base and emitter of  $Q_2$ . Since  $Q_2$  is identical to  $Q_1$ , the emitter current of  $Q_2$  will be equal to emitter current of  $Q_1$  which is approximately equal to Iref

As long as Q2 is maintained in the active region ,its collector current  $I_{C2=I_0}$  will be approximately equal to  $I_{ref}$ .

Since the output current Io is a reflection or mirror of the reference current Iref, the circuit is often referred to as a current mirror.

#### Analysis:

The collector current Ic1 and Ic2 for the transistor Q1 and Q2 can be approximately expressed as

```

V_{BmEmilmi}

IC1 t \alpha_{F} I_{ES} e^{V_{T}} -----(1)

V_{BmEmi2mm}

IC2 t \alpha_{F} I_{ES} e^{V_{T}} -----(2)

From equation (1)&(2)

```

$I_{C2}$   $I_{C1} = e$   $I_{C1} = e$   $I_{C1} = e$   $I_{C1} = e$   $I_{C2} = I_{C1} = I_{C2} = I_{C1} = I_{$

Ic may be expressed as

$$I_C = \beta + 2^I \qquad -----(5)$$

Where Iref from fig can be seen to be  $V_{BE}$   $V_{CC}$   $I_{ref} = V_{CC} @$  fffffffffff  $\approx \approx \frac{V_{CC}}{R_1}$  (as V<sub>BE</sub> =0.7V is small)  $R_1$   $R_1$

From Eq.5 for  $\beta >>1$ ,  $\beta$  is almost unity and the output current I<sub>0</sub> is equal to the reference  $\beta + 2$

current, Iref which for a given R1 is constant. Typically I<sub>0</sub> varies by about 3% for  $50 \le \beta \le 200$ .

It is possible to obtain current transfer ratio other than unity simple by controlling the area of the emitter-base junction (EBJ) of the transistor  $Q_2$ . For example, if the area of EBJ of  $Q_2$  is 4 times that of Q1,then

Io=4 I ref

The output resistance of the current source is the output resistance, ro of Q2,  $\sim - V$

The circuit however operates as a constant current source as long as Q<sub>2</sub> remains in the active region.

# UNIT II Characteristics of op-amp

#### 2.0 General Operational Amplifier:

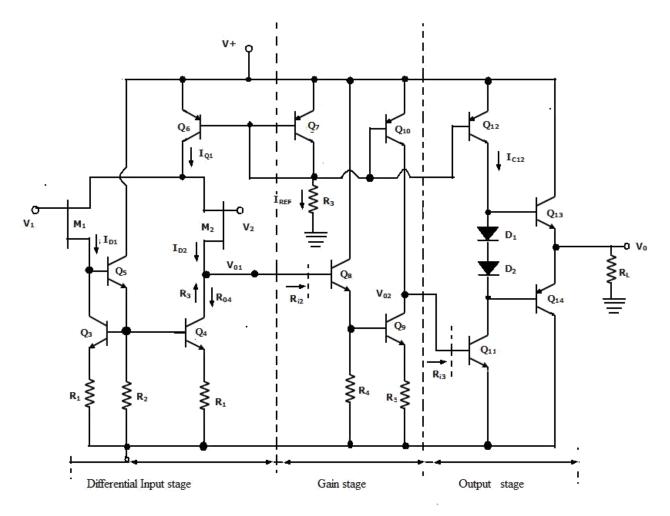

An operational amplifier generally consists of three stages, anmely,1. a differential amplifier 2. additional amplifier stages to provide the required voltage gain and dc level shifting 3. an emitter-follower or source follower output stage to provide current gain and low output resistance.

A low-frequency or dc gain of approximately  $10^4$  is desired for a general purpose op-amp and hence, the use of active load is preferred in the internal circuitry of op-amp. The output voltage is required to be at ground, when the differential input voltages is zero, and this necessitates the use of dual polarity supply voltage. Since the output resistance of op-amp is required to be low, a complementary push-pull emitter – follower or source follower output stage is employed. Moreover, as the input bias currents are to be very small of the order of picoamperes, an FET input stage is normally preferred. The figure shows a general op-amp circuit using JFET input devices.

The input differential amplifier stage uses p-channel JFETs M<sub>1</sub> and M<sub>2</sub>. It employs a three-transistor active load formed by Q<sub>3</sub>, Q<sub>4</sub>, and Q<sub>5</sub>. the bias current for the stage is provided by a two-transistor current source using PNP transistors Q<sub>6</sub> and Q<sub>7</sub>. Resistor R<sub>1</sub> increases the output resistance seen looking into the collector of Q<sub>4</sub> as indicated by R<sub>04</sub>. This is necessary to provide bias current stability against the transistor parameter variations. Resistor R<sub>2</sub> establishes a definite bias current through Q<sub>5</sub>. A single ended output is taken out at the collector of Q<sub>4</sub>.

MOSFET's are used in place of JFETs with additional devices in the circuit to prevent any damage for the gate oxide due to electrostatic discharges.

## Gain stage:

The second stage or the gain stage uses Darlington transistor pair formed by Q<sub>8</sub> and Q<sub>9</sub> as shown in figure. The transistor Q<sub>8</sub> is connected as an emitter follower, providing large input resistance.

Therefore, it minimizes the loading effect on the input differential amplifier stage. The transistor Q9 provides an additional gain and Q10 acts as an active load for this stage. The current mirror formed by Q7 and Q10 establishes the bias current for Q9. The VBE drop across Q9 and drop across R5 constitute the voltage drop across R4, and this voltage sets the current through Q8. It can be set to a small value, such that the base current of Q8 also is very less.

## 2.1.2 Output stage:

The final stage of the op-amp is a class AB complementary push-pull output stage. Q11 is an emitter follower, providing a large input resistance for minimizing the loading effects on the gain stage. Bias current for Q11 is provided by the current mirror formed by Q7 and Q12, through Q13 and Q14 for minimizing the cross over distortion. Transistors can also be used in place of the two diodes.

The overall voltage gain Av of the op-amp is the product of voltage gain of each stage as given by Av = |Ad| |A2| |A3|

Where  $A_d$  is the gain of the differential amplifier stage,  $A_2$  is the gain of the second gain stage and  $A_3$  is the gain of the output stage.

## 2.1 IC 741 Bipolar operational amplifier:

The IC 741 produced since 1966 by several manufactures is a widely used general purpose operational amplifier. Figure shows that equivalent circuit of the 741 op-amp, divided into various individual stages. The op-amp circuit consists of three stages.

- 1. the input differential amplifier

- 2. The gain stage

- 3. the output stage.

A bias circuit is used to establish the bias current for whole of the circuit in the IC. The op-amp is supplied with positive and negative supply voltages of value  $\pm$  15V, and the supply voltages as low as  $\pm$ 5V can also be used.

#### **Bias Circuit:**

The reference bias current IREF for the 741 circuit is established by the bias circuit consisting of two diodes-connected transistors Q11 and Q12 and resistor R5. The widlar current source formed by Q11, Q10 and R4 provide bias current for the differential amplifier stage at the collector of Q10.

ransistors Q<sub>8</sub> and Q<sub>9</sub> form another current mirror providing bias current for the differential amplifier. The reference bias current IREF also provides mirrored and proportional current at the collector of the double –collector lateral PNP transistor Q<sub>13</sub>. The transistor Q<sub>13</sub> and Q<sub>12</sub> thus form a two-output current mirror with Q<sub>13A</sub> providing bias current for output stage and Q<sub>13B</sub> providing bias current for Q<sub>17</sub>. The transistor Q<sub>18</sub> and Q<sub>19</sub> provide dc bias for the output stage. Formed by Q<sub>14</sub> and Q<sub>20</sub> and they establish two VBE drops of potential difference between the bases of Q<sub>14</sub> and Q<sub>18</sub>.

## **Input stage:**

The input differential amplifier stage consists of transistors  $Q_1$  through  $Q_7$  with biasing provided by  $Q_8$  through  $Q_{12}$ . The transistor  $Q_1$  and  $Q_2$  form emitter – followers contributing to high differential input resistance, and whose output currents are inputs to the common base amplifier using  $Q_3$  and  $Q_4$  which offers a large voltage gain.

The transistors Q5, Q6 and Q7 along with resistors R<sub>1</sub>, R<sub>2</sub> and R<sub>3</sub> from the active load for input stage. The single-ended output is available at the collector of Q<sub>6</sub> the two null terminals in the input stage facilitate the null adjustment. The lateral PNP transistors Q<sub>3</sub> and Q<sub>4</sub> provide additional protection against voltage breakdown conditions. The emitter-base junction Q<sub>3</sub> and Q<sub>4</sub> have higher emitter-base breakdown voltages of about 50V. Therefore, placing PNP transistors in series with NPN transistors provide protection against accidental shorting of supply to the input terminals.

## Gain Stage:

The Second or the gain stage consists of transistors  $Q_{16}$  and  $Q_{17}$ , with  $Q_{16}$  acting as an emitter – follower for achieving high input resistance. The transistor  $Q_{17}$  operates in common emitter configuration with its collector voltage applied as input to the output stage. Level shifting is done for this signal at this stage.

Internal compensation through Miller compensation technique is achieved using the feedback capacitor C<sub>1</sub> connected between the output and input terminals of the gain stage.

## **Output stage:**

The output stage is a class AB circuit consisting of complementary emitter follower transistor pair Q14 and Q20. Hence, they provide an effective loss output resistance and current gain.

The output of the gain stage is connected at the base of  $Q_{22}$ , which is connected as an emitter – follower providing a very high input resistance, and it offers no appreciable loading effect on the

gain stage. It is biased by transistor Q13A which also drives Q18 and Q19, that are used for establishing a quiescent bias current in the output transistors Q14 and Q20.

## 2.1.4 Ideal op-amp characteristics:

- 1. Infinite voltage gain A.

- 2. Infinite input resistance R<sub>i</sub>, so that almost any signal source can drive it and there is no loading of the proceeding stage.

- 3. Zero output resistance R<sub>0</sub>, so that the output can drive an infinite number of other devices.

- 4. Zero output voltage, when input voltage is zero.

- 5. Infinite bandwidth, so that any frequency signals from o to  $\infty$  HZ can be amplified with out attenuation.

- 6. Infinite common mode rejection ratio, so that the output common mode noise voltage is zero.

- 7. Infinite slew rate, so that output voltage changes occur simultaneously with input voltage changes.

#### 2.2 AC Characteristics:

For small signal sinusoidal (AC) application one has to know the ac characteristics such as frequency response and slew-rate.

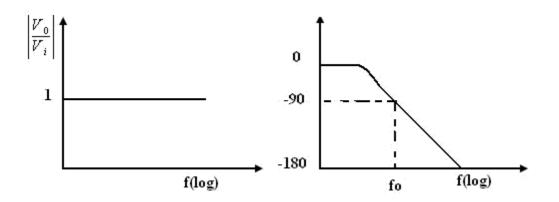

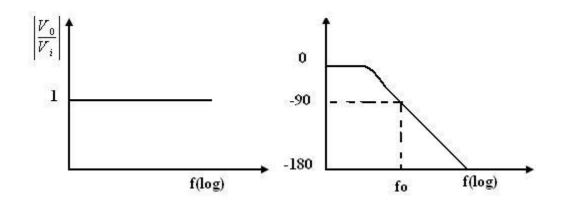

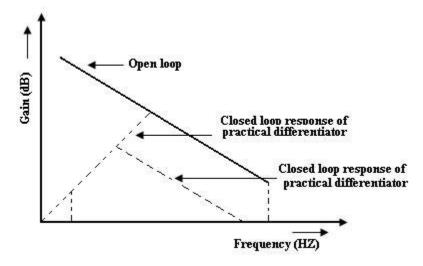

#### **Frequency Response:**

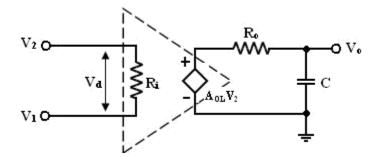

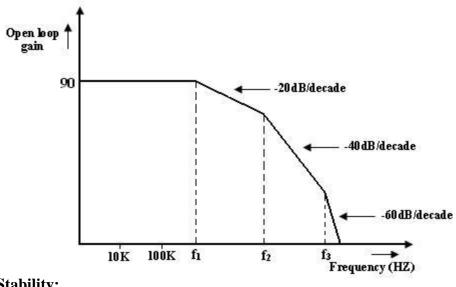

The variation in operating frequency will cause variations in gain magnitude and its phase angle. The manner in which the gain of the op-amp responds to different frequencies is called the frequency response. Op-amp should have an infinite bandwidth  $Bw =\infty$  (i.e) if its open loop gain in 90dB with dc signal its gain should remain the same 90 dB through audio and onto high radio frequency. The op-amp gain decreases (roll-off) at higher frequency what reasons to decrease gain after a certain frequency reached. There must be a capacitive component in the equivalent circuit of the op-amp. For an op-amp with only one break (corner) frequency all the capacitors effects can be represented by a single capacitor C. Below fig is a modified variation of the low frequency model with capacitor C at the o/p.

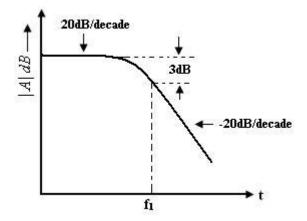

There is one pole due to R<sub>0</sub> C and one -20dB/decade. The open loop voltage gain of an op-amp with only one corner frequency is obtained from above fig.

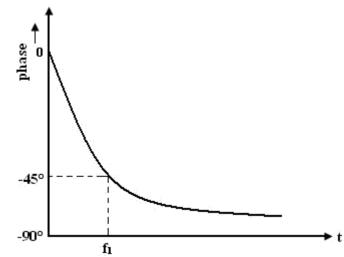

f1 is the corner frequency or the upper 3 dB frequency of the op-amp. The magnitude and phase angle of the open loop volt gain are fu of frequency can be written as,

The magnitude and phase angle characteristics from eqn (29) and (30)

- 1. For frequency  $f \ll f_1$  the magnitude of the gain is 20 log AoL in dB.

- 2. At frequency  $f = f_1$  the gain in 3 dB down from the dc value of AoL in dB. This frequency  $f_1$  is called corner frequency.

- 3. For  $f >> f_1$  the fain roll-off at the rate off -20dB/decade or -6dB/decade.

From the phase characteristics that the phase angle is zero at frequency f = 0.

At the corner frequency f1 the phase angle is  $-45^{0}$  (lagging and a infinite frequency the phase angle is  $-90^{0}$ . It shows that a maximum of  $90^{0}$  phase change can occur in an op-amp with a single capacitor C. Zero frequency is taken as te decade below the corner frequency and infinite frequency is one decade above the corner frequency.

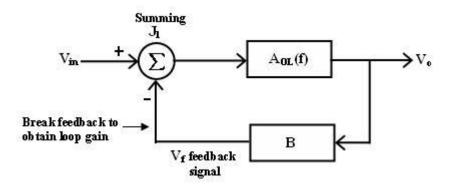

#### 2.1.6 Circuit Stability:

A circuit or a group of circuit connected together as a system is said to be stable, if its o/p reaches a fixed value in a finite time. (or) A system is said to be unstable, if its o/p increases with time instead of achieving a fixed value. In fact the o/p of an unstable sys keeps on increasing until the system break down. The unstable system are impractical and need be made stable. The

criterian gn for stability is used when the system is to be tested practically. In theoretically, always used to test system for stability, ex: Bode plots.

Bode plots are compared of magnitude Vs Frequency and phase angle Vs frequency. Any system whose stability is to be determined can represented by the block diagram.

The block between the output and input is referred to as forward block and the block between the output signal and f/b signal is referred to as feedback block. The content of each block is referred —Transfer frequency' From fig we represented it by AoL (f) which is given by

AoL (f) =  $V_0 / V_{in}$  if  $V_f = 0$ . ----(1)

where  $A_{OL}(f) = open loop volt gain.$  The closed loop gain  $A_f$  is given

by

$$A_F = V_0 / Vin$$

$$A_F = A_{OL} / (1 + (A_{OL}) (B) ----(2))$$

$\mathbf{B} = \text{gain of feedback circuit.}$

B is a constant if the feedback circuit uses only resistive components. Once the magnitude Vs frequency and phase angle Vs frequency plots are drawn, system stability may be determined as follows

## 1. Method:1:

Determine the phase angle when the magnitude of (AoL) (B) is 0dB (or) 1. If phase angle is >  $.-180^{0}$ , the system is stable. However, the some systems the magnitude may never be 0, in that cases method 2, must be used.

## 2. Method 2:

Determine the phase angle when the magnitude of (AoL) (B) is 0dB (or) 1. If phase angle is > .- 180<sup>0</sup>, If the magnitude is –ve decibels then the system is stable. However, the some systems the

phase angle of a system may reach  $-180^0$ , under such conditions method 1 must be used to determine the system stability.

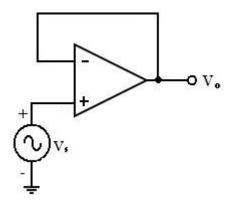

# 2.3 Slew Rate:

Another important frequency related parameter of an op-amp is the slew rate. (Slew rate is the maximum rate of change of output voltage with respect to time. Specified in  $V/\mu s$ ).

# 2.1.8 Reason for Slew rate:

There is usually a capacitor within 0, outside an op-amp oscillation. It is this capacitor which prevents the o/p voltage from fast changing input. The rate at which the volt across the capacitor increases is given by

dVc/dt = I/C ---- (1)

I -> Maximum amount furnished by the op-amp to capacitor C. Op-amp should have the either a higher current or small compensating capacitors.

For 741 IC, the maximum internal capacitor charging current is limited to about  $15\mu$ A. So the slew rate of 741 IC is

SR = dVc/dt |max = Imax/C.

For a sine wave input, the effect of slew rate can be calculated as consider volt follower -> The input is large amp, high frequency sine wave .

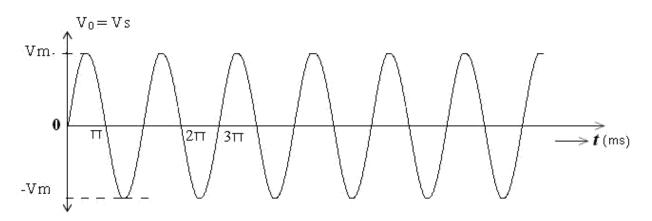

If Vs = Vm Sinwt then output  $V_0 = Vm$  sinwt . The rate of change of output is given by  $dV_0/dt = Vm$  w coswt.

## Input and Output Waveforms

The max rate of change of output across when  $\cos wt = 1$

(i.e)  $SR = dV_0/dt | max = wVm.$

$SR = 2\prod fVm V/s = 2\prod fVm v/ms.$

Thus the maximum frequency fmax at which we can obtain an undistorted output volt of peak value Vm is given by

fmax (Hz) = Slew rate/6.28 \* Vm.

called the full power response. It is maximum frequency of a large amplitude sine wave with which op-amp can have without distortion.

## 2.4 DC Characteristics of op-amp:

Current is taken from the source into the op-amp inputs respond differently to current and voltage due to mismatch in transistor.

DC output voltages are,

- 1. Input bias current

- 2. Input offset current

- 3. Input offset voltage

- 4. Thermal drift

$\triangleright$

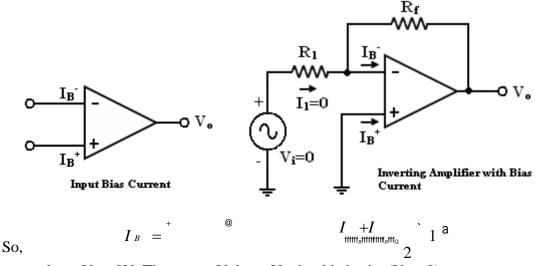

## **2.1.10 Input bias current:**

The op-amp's input is differential amplifier, which may be made of BJT or FET.

In an ideal op-amp, we assumed that no current is drawn from the input terminals.

The base currents entering into the inverting and non-inverting terminals ( $IB^- \& IB^+$  respectively).

Even though both the transistors are identical,  $IB^-$  and  $IB^+$  are not exactly equal due to internal imbalance between the two inputs.

Manufacturers specify the input bias current IB

If input voltage  $V_i = 0V$ . The output Voltage  $V_o$  should also be  $(V_o = 0)$ IB = 500nA We find that the output voltage is offset by,

> b <u>e</u> ` a  $V_o = I_B R_f Q 2$

Op-amp with a 1M feedback resistor

$V_0 = 5000nA X 1M = 500mV$

The output is driven to 500mV with zero input, because of the bias currents.

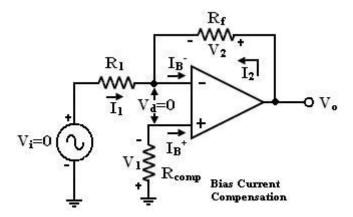

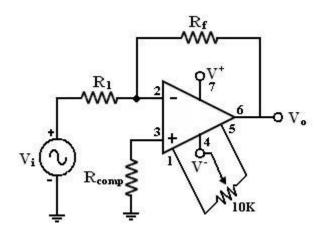

In application where the signal levels are measured in mV, this is totally unacceptable. This can be compensated. Where a compensation resistor  $R_{comp}$  has been added between the non-inverting input terminal and ground as shown in the figure below.

Current  $IB^+$  flowing through the compensating resistor  $R_{comp}$ , then by KVL we get,

$$-V_1+0+V_2-V_0 = 0$$

(or)

$V_0 = V_2 - V_1 \longrightarrow (3)$

By selecting proper value of  $R_{comp}$ ,  $V_2$  can be cancelled with  $V_1$  and the  $V_0 = 0$ . The value of  $R_{comp}$  is derived a

$$V_1 = I_B^+ R_{comp} \text{ (or)}$$

$$I_B^+ = V_1/R_{comp} \longrightarrow (4)$$

The node =a' is at voltage (-V<sub>1</sub>). Because the voltage at the non-inverting input terminal is (-V<sub>1</sub>). So with  $V_i = 0$  we get,

$$I_1 = V_1/R_1 \longrightarrow (5)$$

$I_2 = V_2/R_f \longrightarrow (6)$

For compensation,  $V_0$  should equal to zero ( $V_0 = 0$ ,  $V_i = 0$ ). i.e. from equation (3)  $V_2 = V_1$ . So that,

$$I_2 = V_1/R_f ---->(7)$$

KCL at node =a' gives,

$$IB = I2 + I1$$

$$I_B = R_{f R_1}$$

Assume  $IB^{-} = IB^{+}$  and using equation (4) & (8) we get

$$R^{comp} = R_1 + R_f$$

$R_{comp} = R_1 || R_f \longrightarrow (9)$

i.e. to compensate for bias current, the compensating resistor,  $R_{comp}$  should be equal to the parallel combination of resistor  $R_1$  and  $R_f$ .

#### **2.1.11 Input offset current:**

Bias current compensation will work if both bias currents  $IB^+$  and  $IB^-$  are equal.

$\geqslant$

Since the input transistor cannot be made identical. There will always be some small difference between  $IB^+$  and  $IB^-$ . This difference is called the offset current

+

$|I_{os}| = I_{B}^{+} - I_{B}^{-} \longrightarrow (10)$

Offset current I<sub>os</sub> for BJT op-amp is 200nA and for FET op-amp is 10pA. Even with bias current compensation, offset current will produce an output voltage when  $V_i = 0$ .

$V_1 = IB^+ R_{comp} \xrightarrow{} (11)$ And  $I_1 = V_1/R_1 \xrightarrow{} (12)$ KCL at node =a' gives,

Again

$\mathbf{V}_0 = \mathbf{I}_2 \ \mathbf{R}_f - \mathbf{V}_1$

$V_{o} = I_{2} R_{f} - I_{B}^{+} R_{comp}$

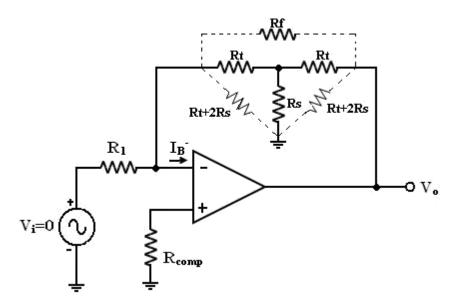

Equation (16) the offset current can be minimized by keeping feedback resistance small.

$\checkmark$  Unfortunately to obtain high input impedance, R<sub>1</sub> must be kept large.

R1 large, the feedback resistor Rf must also be high. So as to obtain reasonable gain.

The T-feedback network is a good solution. This will allow large feedback resistance, while

keeping the resistance to ground low (in dotted line).

The T-network provides a feedback signal as if the network were a single feedback resistor. By T to  $\Pi$  conversion,

To design T- network first pick  $R_t << R_f/2 \longrightarrow (18)$ Then calculate  $R_s = R_f 2 R_f$

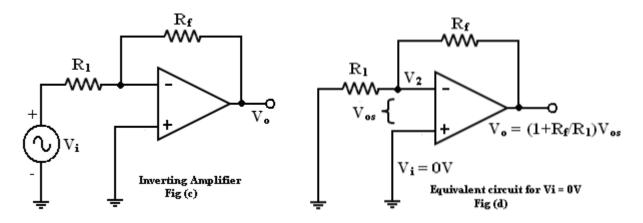

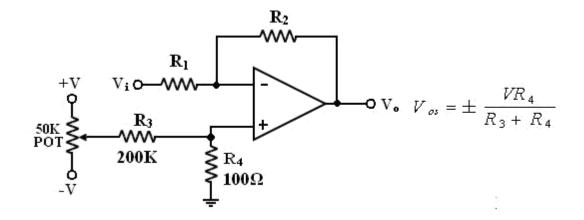

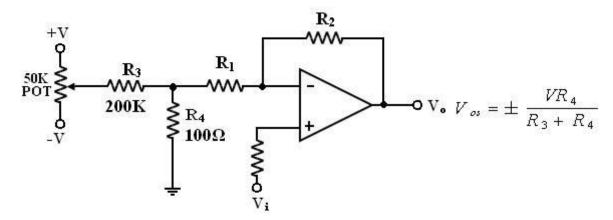

## 2.1.12 Input offset voltage:

Inspite of the use of the above compensating techniques, it is found that the output voltage may still not be zero with zero input voltage  $[V_0 \neq 0 \text{ with } V_i = 0]$ . This is due to unavoidable imbalances inside the op-amp and one may have to apply a small voltage at the input terminal to make output  $(V_0) = 0$ .

This voltage is called input offset voltage  $V_{os}$ . This is the voltage required to be applied at the input for making output voltage to zero ( $V_o = 0$ ).

Let us determine the  $V_{os}$  on the output of inverting and non-inverting amplifier. If  $V_i = 0$  (Fig (b) and (c)) become the same as in figure (d).

#### Total output offset voltage:

The total output offset voltage Vor could be either more or less than the offset voltage produced at the output due to input bias current (IB) or input offset voltage alone(Vos).

This is because I<sub>B</sub> and  $V_{os}$  could be either positive or negative with respect to ground. Therefore the maximum offset voltage at the output of an inverting and non-inverting amplifier (figure b, c) without any compensation technique used is given by many op-amp provide offset compensation

pins to nullify the offset voltage.

$\geqslant$

10K potentiometer is placed across offset null pins 1&5. The wipes connected to the

- negative supply at pin 4.

- The position of the wipes is adjusted to nullify the offset voltage.

When the given (below) op-amps does not have these offset null pins, external balancing techniques are used.

2.5 Non-inverting amplifier:

## **Thermal drift:**

Bias current, offset current, and offset voltage change with temperature.

A circuit carefully nulled at 25°C may not remain. So when the temperature rises to 35°C. This is called drift.

Offset current drift is expressed in nA/°C.

These indicate the change in offset for each degree Celsius change in temperature.

# 2.1.14 Openloop-op-amp Configuration:

The term open-loop indicates that no feedback in any form is fed to the input from the output. When connected in open - loop, the op-amp functions as a very high gain amplifier. There are three open - loop configurations of op-amp namely,

- 1. differential amplifier

- 2. Inverting amplifier

- 3. Non-inverting amplifier

The above classification is made based on the number of inputs used and the terminal to which the input is applied. The op-amp amplifies both ac and dc input signals. Thus, the input signals can be either ac or dc voltage.

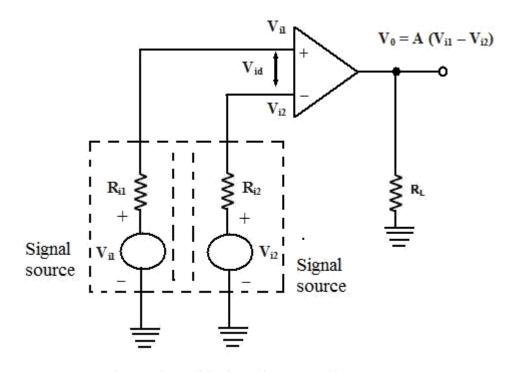

# 2.1.15 Open-loop Differential Amplifier:

In this configuration, the inputs are applied to both the inverting and the non-inverting input terminals of the op-amp and it amplifies the difference between the two input voltages. Figure shows the open-loop differential amplifier configuration.

The input voltages are represented by V<sub>i1</sub> and V<sub>i2</sub>. The source resistance R<sub>i1</sub> and R<sub>i2</sub> are negligibly small in comparison with the very high input resistance offered by the op-amp, and thus the voltage drop across these source resistances is assumed to be zero. The output voltage V<sub>0</sub> is given by

$V_0 = A(V_{i1} - V_{i2})$ where A is the large signal voltage gain. Thus the output voltage is equal to the voltage gain A

times the difference between the two input voltages. This is the reason why this configuration is called a differential amplifier. In open – loop configurations, the large signal voltage gain A is also called open-loop gain A.

Open - loop Differential Amplifier

2.6 Inverting amplifier:

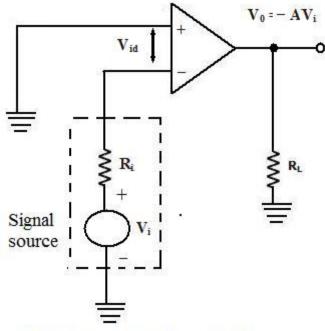

Open - loop Inverting Amplifier

In this configuration the input signal is applied to the inverting input terminal of the op-amp and the non-inverting input terminal is connected to the ground. Figure shows the circuit of an open – loop inverting amplifier. The output voltage is  $180^0$  out of phase with respect to the input and hence, the output voltage  $V_0$  is given by,

$V_0 = -AV_i$

Thus, in an inverting amplifier, the input signal is amplified by the open-loop gain A and in phase - shifted by  $180^{\circ}$ .

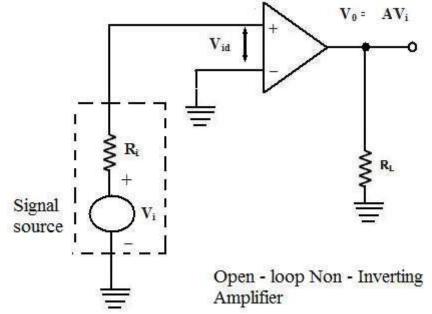

# 2.1.17 Non-inverting Amplifier:

Figure shows the open – loop non- inverting amplifier. The input signal is applied to the non-inverting input terminal of the op-amp and the inverting input terminal is connected to the ground.

The input signal is amplified by the open – loop gain A and the output is in-phase with input signal.

$$V_0 = AV_i$$

In all the above open-loop configurations, only very small values of input voltages can be applied. Even for voltages levels slightly greater than zero, the output is driven into saturation, which is observed from the ideal transfer characteristics of op-amp shown in figure. Thus, when operated in the open-loop configuration, the output of the op-amp is either in negative or positive saturation, or switches between positive and negative saturation levels. This prevents the use of open – loop configuration of op-amps in linear applications.

#### 2.2.1 Limitations of Open – loop Op – amp configuration:

Firstly, in the open – loop configurations, clipping of the output waveform can occur when the output voltage exceeds the saturation level of op-amp. This is due to the very high open – loop gain of the op-amp. This feature actually makes it possible to amplify very low frequency signal of the order of microvolt or even less, and the amplification can be achieved accurately without any distortion. However, signals of such magnitudes are susceptible to noise and the amplification for those application is almost impossible to obtain in the laboratory.

Secondly, the open – loop gain of the op – amp is not a constant and it varies with changing temperature and variations in power supply. Also, the bandwidth of most of the open- loop op amps is negligibly small. This makes the open – loop configuration of op-amp unsuitable for ac applications. The open – loop bandwidth of the widely used 741 IC is approximately 5Hz. But in almost all ac applications, the bandwidth requirement is much larger than this.

For the reason stated, the open - loop op-amp is generally not used in linear applications. However, the open - loop op amp configurations find use in certain non - linear applications such as comparators, square wave generators and astable multivibrators.

#### 2.2.2 Closed – loop op-amp configuration:

The op-amp can be effectively utilized in linear applications by providing a feedback from the output to the input, either directly or through another network. If the signal feedback is out- of-phase by  $180^{0}$  with respect to the input, then the feedback is referred to as negative feedback or degenerative feedback. Conversely, if the feedback signal is in phase with that at the input, then the feedback is referred to as positive feedback or regenerative feedback.

An op – amp that uses feedback is called a closed – loop amplifier. The most commonly used closed – loop amplifier configurations are 1. Inverting amplifier (Voltage shunt amplifier) 2. Non-Inverting amplifier (Voltage – series Amplifier)

#### **2.2.3 Inverting Amplifier:**

The inverting amplifier is shown in figure and its alternate circuit arrangement is shown in figure, with the circuit redrawn in a different way to illustrate how the voltage shunt feedback is achieved. The input signal drives the inverting input of the op - amp through resistor  $R_1$ .

The op – amp has an open – loop gain of A, so that the output signal is much larger than the error voltage. Because of the phase inversion, the output signal is  $180^0$  out – of – phase with the input signal. This means that the feedback signal opposes the input signal and the feedback is negative or degenerative.

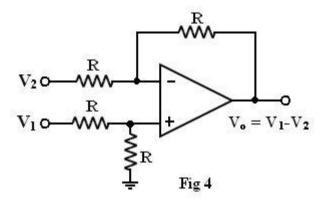

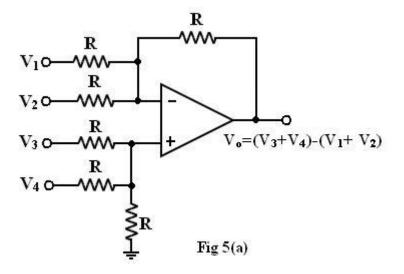

### 3.1 Differential amplifier:

We will evaluate 2 different arrangements of the differential amplifier with -ve feedback. Classify these arrangements according to the number of op-amps used. i.e

- 1. Differential amplifier with one op-amp

- 2. Differential amplifier with two op-amps.

Differential amplifier are used in instrumentation and industrial applications to amplify differences between 2 input signals such as output of the wheat stone bridge circuit.

Differential amplifier preferred to these application because they are better able to reject common mode (noise) voltages than single input circuit such as inverting and non-inverting amplifier.

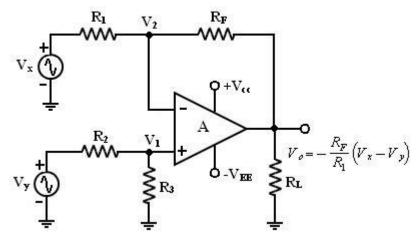

## 2.2.5 Differential Amplifier with one op-amp:

To analyse this circuit by deriving voltage gain and input resistance. This circuit is a combination of inverting and non-inverting amplifier. (i.e) When  $V_x$  is reduced to zero the circuit is non-inverting amplifier and when  $V_y$  is reduced to zero the circuit is inverting amplifier.

## 2.2.6 Voltage Gain:

The circuit has 2 inputs  $V_x$  and  $V_y$ . Use superposition theorem, when  $V_y = 0V$ , becomes inverting amplifier. Hence the o/p due to  $V_x$  only is

Similarly, when  $V_x = 0V$ , becomes Non-inverting amplifier having a voltage divider network composed of R<sub>2</sub> and R<sub>3</sub> at the Non – inverting input.

Note : the gain of the differential amplifier is same as that of inverting amplifier.

## 2.2.7 Input Resistance:

The input resistance R<sub>if</sub> of the differential amplifier is resistance determined looking into either one of the 2 input terminals with the other grounded,

With  $V_y = 0V$ ,

Inverting amplifier, the input resistance which is,

$RiFx \approx R_1$  -----

(26.a) Similarly,  $V_x = 0V$ ,

Non-inverting amplifier, the input resistance which is,

$RiFy \approx (R_2 + R_3)$  -----(26.b)

$V_x$  and  $V_y$  are not the same. Both the input resistance can be made equal, if we modify the basic differential amplifier. Both R<sub>1</sub> and (R<sub>2</sub> + R<sub>3</sub>) can be made much larger than the source resistances. So that the loading of the signal sources does not occur.

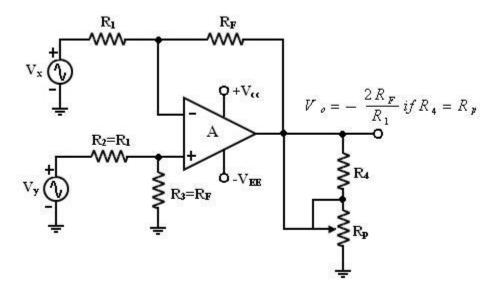

Note: If we need a variable gain, we can use the differential amplifier. In this circuit  $R_1 = R_2$ ,  $R_F = R_3$  and the potentiometer  $R_p = R_4$ .

Depending on the position of the wiper in R voltage can be varied from the closed loop gain of  $-2R_F/R_1$  to the open loop gain of A.

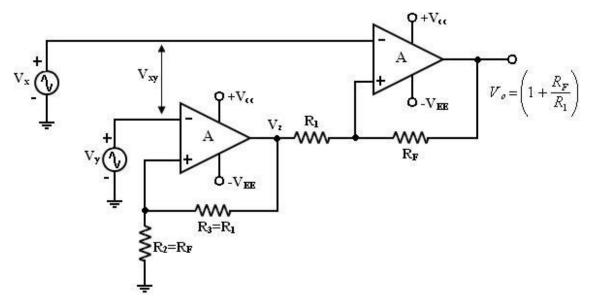

# 2.2.8. Differential Amplifier with 2 op-amps:

We can increase the gain of the differential amplifier and also increase the input resistance R<sub>if</sub> if we use 2 op-amps.

# 2.2.9 Voltage gain:

It is compares of 2 stages 1. Non-inverting

. Differential amplifier with gain.

By finding the gain of these 2 stages, we can obtain the overall gain of the circuit,

## 2.2.10 Input Resistance:

The input resistance Rif of the differential amplifier is the resistance determined from either one of the two non-inverting terminals with the other grounded. The first stage A<sub>1</sub> is the non-inverting amplifier, its input resistance is

RiFy = Ri (1+AB) -----(29. a)

Where Ri = open loop input resistance of the op-amp.

```

B = R_2/R_2 + R_3

```

Similarly, with  $V_y$  shorted to ground ( $V_y = 0$  V), the 2<sup>nd</sup> stage (A<sub>2</sub>) also becomes non-inverting amplifier, whose input resistance is

RiFx = Ri (1+AB) -----(29. b)

Where Ri = open loop input resistance of the op-

amp B = R<sub>1</sub> /(R<sub>1</sub> + R<sub>F</sub>)

Since  $R_1 = R_3$  and  $R_F = R_2$ , the Rify  $\neq$  RiFx because the loading of the input sources  $V_x$  and  $V_y$  may occur. (Or)

The output signal may be smaller in amplitude than expected. This possible reduction in the amplitude of the output signal is drawback of differential amplifier. To overcome this:

With proper selection of components, both RiFy and RiFx can be made much larger than the sources resistance so that the loading of the input sources does not occur.

# **2.2.11** Output resistance and Bandwidth of differential amplifier with feedback:

The output resistance of the differential amplifier should be the same as that of the non-

inverting amplifier expect that  $\mathbf{B} = 1/A_D$  (i.e)

$R_{OF} = R_0 / (1 + A/A_D)$  ----- (30)

$A_D = closed loop gain of the differential amplifier$

$R_0 = output resistance of the op-amp$

A = open - loop volt gain of the op-amp

Remember that AD is different for differential amplifier. In the case of Inverting and Non-inverting amplifier, the bandwidth of the differential amplifier also depends on the closed loop gain of the amplifier and is given by,

$f_F = Unity$  gain Bandwidth closed loop gain AD (or)  $f_F = (A) (f_0)$

#### UNIT III

#### **3.1 APPLICATION OF OP-AMP**

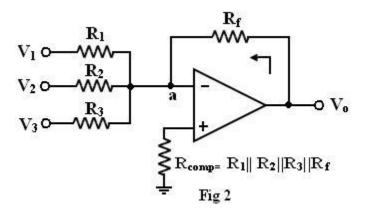

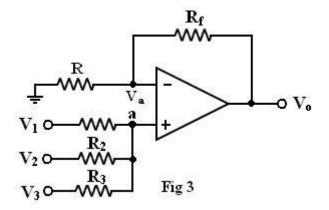

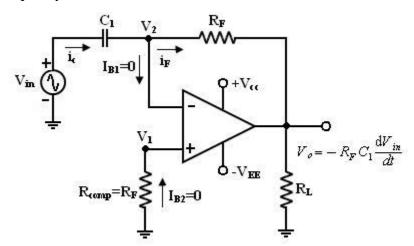

The basic inverting amplifier configuration using an op-amp with input impedance Z  $_1$  and feedback impedance Z  $_f$ .

If the impedance  $Z_1$  and  $Z_f$  are equal in magnitude and phase, then the closed loop voltage gain is -1,and the input signal will undergo a  $180^0$  phase shift at the output. Hence, such circuit is also called phase inverter. If two such amplifiers are connected in cascade, then the output from the second stage is the same as the input signal without any change of sign.

Hence, the outputs from the two stages are equal in magnitude but opposite in phase and such a system is an excellent paraphase amplifier

Referring the above diagram, if the ratio  $Z_f / Z_1 = k$ , a real constant, then the closed loop gain is -k, and the input voltage is multiplied by a factor -k and the scaled output is available at the output. Usually, in such applications,  $Z_f$  and  $Z_1$  are selected as precision resistors for obtaining precise and scaled value of input voltage.

## **3.1.2 PHASE SHIFT CIRCUITS**

The phase shift circuits produce phase shifts that depend on the frequency and maintain a constant gain. These circuits are also called constant-delay filters or all-pass filters. That constant delay refers to the fact the time difference between input and output remains constant when frequency is changed over a range of operating frequencies.

This is called all-pass because normally a constant gain is maintained for all the frequencies within the operating range. The two types of circuits, for lagging phase angles and leading phase angles.

#### 3.1.3 Phase-lag circuit:

Phase log circuit is constructed using an op-amp, connected in both inverting and non inverting modes. To analyze the circuit operation, it is assumed that the input voltage v1 drives a simple inverting amplifier with inverting input applied at(-)terminal of op-amp and a non inverting amplifier with a low-pass filter.

It is also assumed that inverting gain is -1 and non-inverting gain after the low-pass circuit

The relationship is complex as defined above equation and it shows that it has both magnitude and phase. Since the numerator and denominator are complex conjugates, their

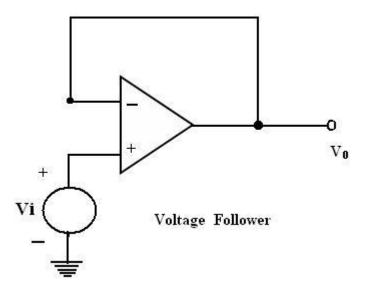

# **3.2 Voltage follower:**

If  $R_1 = \infty$  and  $R_f = 0$  in the non inverting amplifier configuration . The amplifier act as a unity-gain amplifier or voltage follower. That is

> $= 1 + R^{f}$ R

$_{v}A$

Since

$$R = 1$$

$R_1$   $R = 1$

The circuit consist of an op-amp and a wire connecting the output voltage to the input ,i.e the output voltage is equal to the input voltage, both in magnitude and phase. $V_0=V_i$

Since the output voltage of the circuit follows the input voltage, the circuit is called voltage follower. It offers very high input impedance of the order of M $\Omega$  and very low output impedance.

Therefore, this circuit draws negligible current from the source. Thus, the voltage follower can be used as a buffer between a high impedance source and a low impedance load for impedance matching applications.

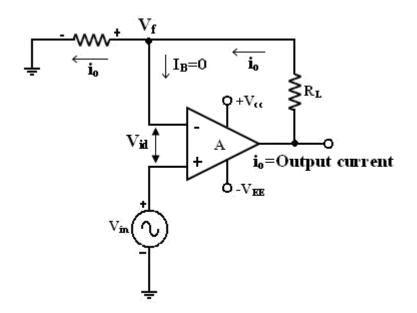

#### 3.1.5 Voltage to Current Converter with floating loads (V/I):

- 1. Voltage to current converter in which load resistor RL is floating (not connected to ground).

- 2. Vin is applied to the non inverting input terminal, and the feedback voltage across R1 devices the inverting input terminal.

- 3. This circuit is also called as a current series negative feedback amplifier.

- 4. Because the feedback voltage across R1 (applied Non-inverting terminal) depends on the output current io and is in series with the input difference voltage Vid .

Writing KVL for the input loop,

$$Vin = V_{id} + V_f$$

$$V_{id} \quad 0v, since A is very large A$$

$$Vin = V_f$$

$$Vin = R_1 i_0 \quad or^{a}$$

From the fig input voltage Vin is converted into output current of Vin/R<sub>1</sub> [Vin -> i0]. In other words, input volt appears across R<sub>1</sub>. If R<sub>1</sub> is a precision resistor, the output current (i0 = Vin/R<sub>1</sub>) will be precisely fixed.

# **Applications:**

- 1. Low voltage ac and dc voltmeters

- 2. Diode match finders

- 3. LED

- 4. Zener diode testers.

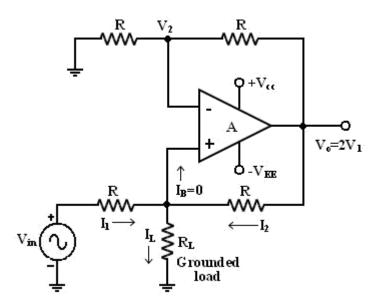

## 3.1.6 Voltage – to current converter with Grounded load:

This is the other type V – I converter, in which one terminal of the load is connected to ground.

## Analysis of the circuit:

The analysis of the circuit can be done by following 2 steps.

- 1. To determine the voltage  $V_1$  at the non-inverting (+) terminals and

- 2. To establish relationship between  $V_1$  and the load current IL

- . Applying KCL at node  $V_1$  we can write that,

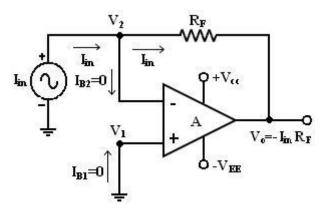

# 3.3 Current to Voltage Converter (I –V):

- 1. Open loop gain a of the op-amp is very large.  $V_1 \approx V_2$  @@@@ $1^a$

- 2. Input impedance of the op-amp is very high. (i.e) the currents entering into the 2 input

terminals is very small.  $I_{B}$

$=I_{B_{2}}$

#### 3.1.8 Sensitivity of the I – V converter:

- 1. The output voltage  $V_0 = -R_F I_{in}$ .

- 2. Hence the gain of this converter is equal to -RF. The magnitude of the gain (i.e) is also called as sensitivity of I to V converter.

- 3. The amount of change in output volt  $\Delta V_0$  for a given change in the input current  $\Delta I$  in is decide by the sensitivity of I-V converter.

- 4. By keeping RF variable, it is possible to vary the sensitivity as per the requirements.

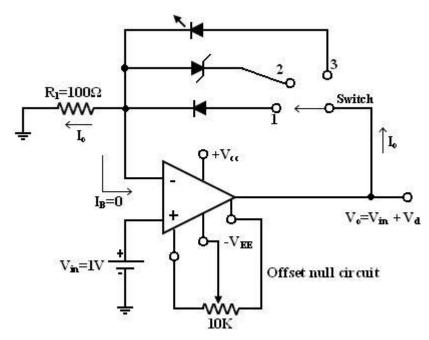

#### 3.1.9 Applications of V-I converter with Floating Load:

## 1. Diode Match finder:

In some applications, it is necessary to have matched diodes with equal voltage drops at a particular value of diode current. The circuit can be used in finding matched diodes and is obtained from fig (V-I converter with floating load) by replacing RL with a diode. When the switch is in position 1: (Diode Match Finder) Rectifierr diode (IN 4001) is placed in the f/b loop, the current through this loop is set by input voltage Vin and Resistor R<sub>1</sub>. For Vin = 1V and R<sub>1</sub> = 100 $\Omega$ , the current through this

$$I_0 = Vin/R_1 = 1/100 = 10mA_1$$

As long as V<sub>0</sub> and R<sub>1</sub> constant, I<sub>0</sub> will be constant. The Voltage drop across the diode can be found either by measuring the volt across it or o/p voltage. The output voltage is equal to (Vin + V<sub>D</sub>) V<sub>0</sub>

= Vin + V<sub>D</sub>. To avoid an error in output voltage the op-amp should be initially nulled. Thus the matched diodes can be found by connecting diodes one after another in the feedback path and measuring voltage across them.

#### 2. Zener diode Tester:

(When the switch position 2)

when the switch is in position 2, the circuit becomes a zener diode tester. The circuit can be used to find the breakdown voltage of zener diodes. The zener current is set at a constant value by Vin and R<sub>1</sub>. If this current is larger than the knee current (Iz $\kappa$ ) of the zener, the zener blocks (V<sub>z</sub>) volts. For Ex:

$I_{ZK} = 1 mA$ ,  $V_Z = 6.2V$ ,  $V_{in} = 1v$ ,  $R_1 = 100\Omega$  Since the current through the zener is,  $I_0 = Vin/R_1 = 1/100 = 10 mA > I_{ZK}$  the voltage across the zener will be approximately equal to 6.2V.

## **3.** When the switch is in position **3**: (LED)

The circuit becomes a LED when the switch is in position 3. LED current is set at a constant value by Vin and R<sub>1</sub>. LEDs can be tested for brightness one after another at this current. Matched LEDs with equal brightness at a specific value of current are useful as indicates and display devices in digital applications.

#### 3.1.10 Applications of I – V Converter:

One of the most common use of the current to voltage converter is

- 1. Digital to analog Converter (DAC)

- 2. Sensing current through Photodetector. Such as photocell, photodiodes and photovoltaic cells.

Photoconductive devices produce a current that is proportional to an incident energy or light (i.e) It can be used to detect the light.

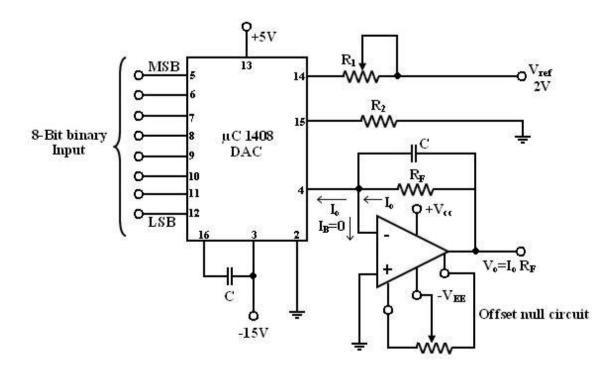

### 3.1.11 DAC using I – V converter:

It shows a combination of a DAC and current to voltage converter. The 8 digit binary signal is the input to the DAC and V<sub>0</sub> is the corresponding analog output of the current to voltage converter. The outputu of the DAC is current I<sub>0</sub>, the value of which depends on the logic state (0 or 1), of the binary inputs as indicated by the following eqn.

This means I<sub>0</sub> is zero when all inputs are logic 0.

Io is max when all inputs are logic 1.

The variations in I<sub>0</sub> can be converted into a desired o/p voltage range by selecting a proper value for R<sub>F</sub>. since, V<sub>0</sub> = I<sub>0</sub> R<sub>F</sub>

Where I<sub>0</sub> is given by eqn (1). It is common to parallel R<sub>F</sub> with capacitance C to minimize the overshoot. In the fig the o/p voltage of the current to voltage converter is positive because the direction of input current I<sub>0</sub> is opposite to that in the basic I – V Converter.

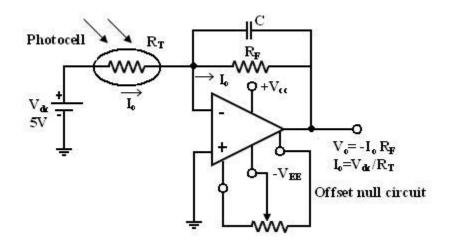

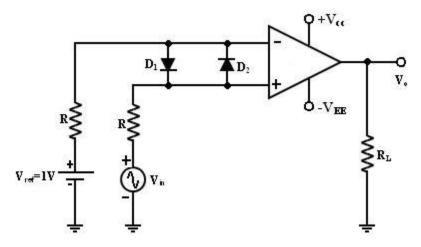

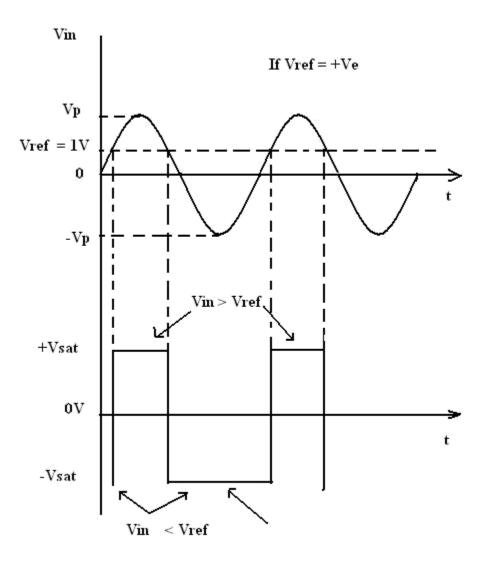

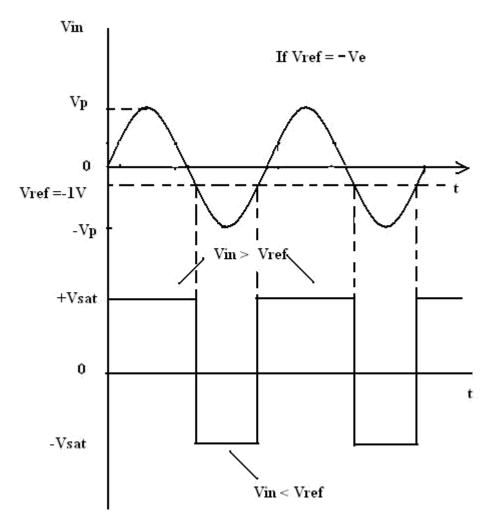

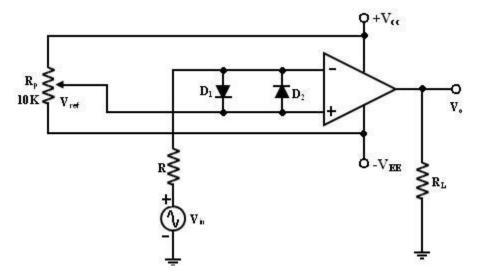

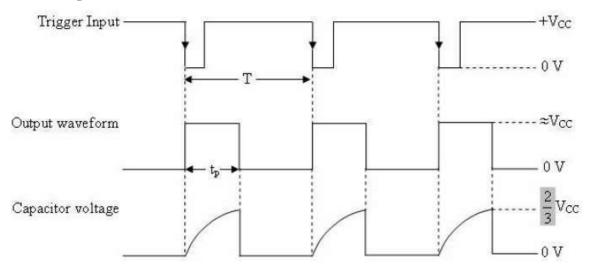

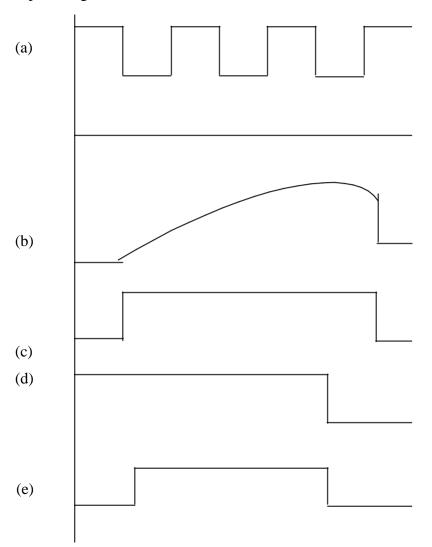

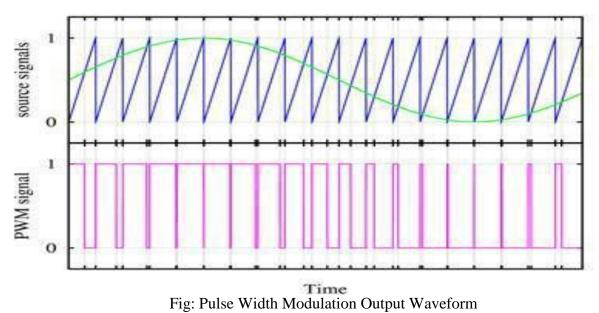

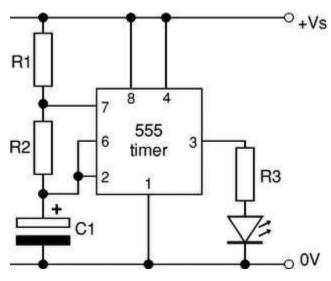

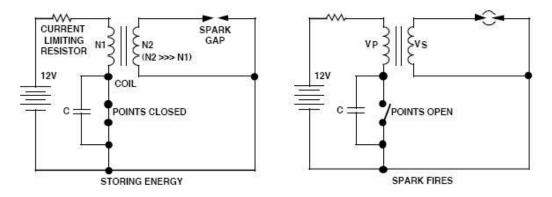

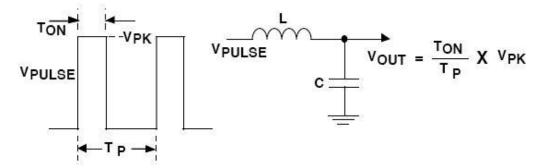

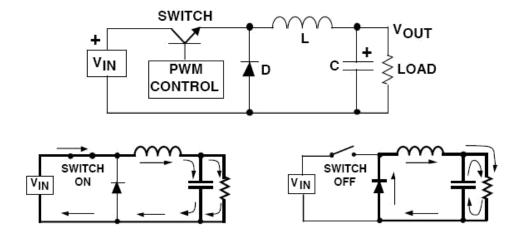

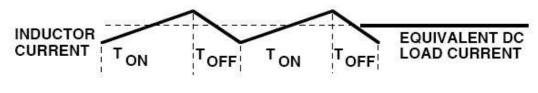

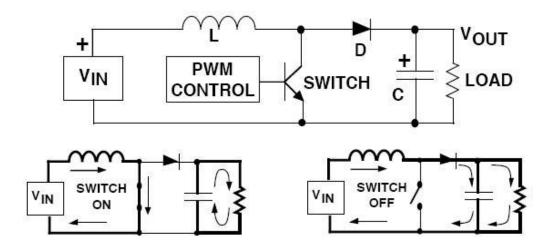

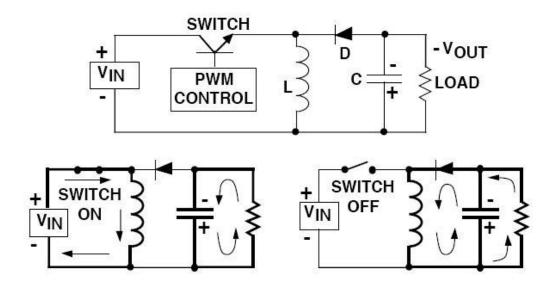

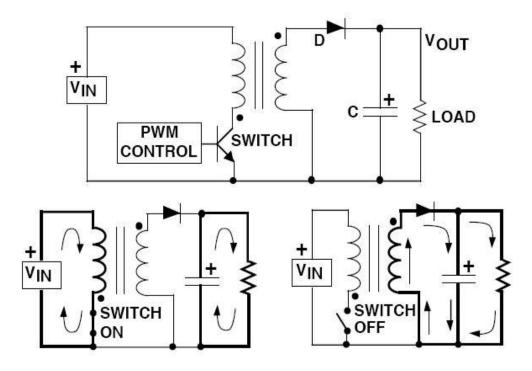

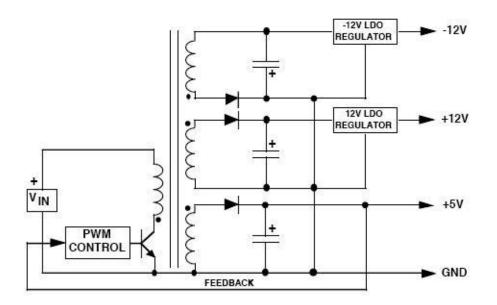

2. Detecting current through photosensitive devices: