A Course Material on

# Embedded Systems

Ву

#### Mr.E.DILLIRAJ

#### ASSISTANT PROFESSOR

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

## PRATHYUSHA ENGINEERING COLLEGE

| TABLE OF CONTENT |                                          |                 |

|------------------|------------------------------------------|-----------------|

| S.NO             | TOPICS                                   | PAGE NO         |

|                  | UNIT I INTRODUCTION TO EMBEDDED COMPUT   | TING            |

| 1.1              | COMPLEX SYSTEMS AND MICROPROCESSORS      | 1               |

| 1.2              | DESIGN EXAMPLE: MODEL TRAIN CONTROLLER   | 5               |

| 1.3              | EMBEDDED SYSTEM DESIGN PROCESS           | 12              |

| 1.4              | FORMALISM FOR SYSTEM DESIGN              | 17              |

| 1.5              | INSTRUCTION SETS PRELIMINARIES           | 21              |

| 1.6              | ARM PROCESSOR                            |                 |

| 1.7              | CPU: PROGRAMMING INPUT AND OUTPUT        | 25<br>30        |

| 1.8              | SUPERVISOR MODE, EXCEPTION AND TRAPS     | 31              |

| 1.10             | COPROCESSOR                              | 33              |

| 1.11             | MEMORY SYSTEM MECHANISM                  | 34              |

| 1.12             | CPU PERFORMANCE                          | 20              |

| 1.13             | CPU POWER CONSUMPTION                    | <u>38</u><br>40 |

|                  | UNIT II COMPUTING PLATFORM AND DESIGN AN | ALYSIS          |

| 2.1              | CPU BUSES                                | 41              |

| 2.2              | MEMORY DEVICES                           | 45              |

| 2.3              | I/O DEVICES                              | 48              |

| 2.4              | COMPONENT INTERFACING                    | 52              |

| 2.5              | DESIGN WITH MICROPROCESSORS              | 53              |

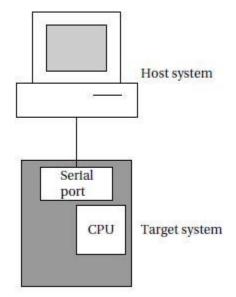

| 2.6              | DEVELOPMENT AND DEBUGGING                | 55              |

| 2.7              | PROGRAM DESIGN                           | <u> </u>        |

| 2.8              | MODEL OF PROGRAMS                        | <b>5</b> 0      |

| 2.9              | ASSEMBLY AND LINKING                     | <u>58</u><br>59 |

| 2.10                                          | BASIC COMPILATION TECHNIQUES                                                                                                                                                                                                                                                                                                                                  | 62                                            |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.11                                          | ANALYSIS AND OPTIMIZATION OF EXECUTION                                                                                                                                                                                                                                                                                                                        | 02                                            |

|                                               | TIME, POWER, ENERGY, PROGRAM SIZE                                                                                                                                                                                                                                                                                                                             | 64                                            |

| 2.12                                          | PROGRAM VALIDATION AND TESTING                                                                                                                                                                                                                                                                                                                                | 65                                            |

|                                               | UNIT III PROCESS AND OPERATING SYSTEMS                                                                                                                                                                                                                                                                                                                        |                                               |

| 3.1                                           | MULTIPLE TASKS AND MULTI PROCESSES                                                                                                                                                                                                                                                                                                                            |                                               |

|                                               |                                                                                                                                                                                                                                                                                                                                                               | 67                                            |

| 3.2                                           | PROCESSES & CONTEXT SWITCHING                                                                                                                                                                                                                                                                                                                                 | 71                                            |

| 3.3                                           | OPERATING SYSTEMS                                                                                                                                                                                                                                                                                                                                             | 72                                            |

| 3.4                                           | SCHEDULING POLICIES                                                                                                                                                                                                                                                                                                                                           | 72                                            |

| 3.5                                           | MULTIPROCESSOR                                                                                                                                                                                                                                                                                                                                                |                                               |

|                                               |                                                                                                                                                                                                                                                                                                                                                               | 74                                            |

| 3.6                                           | INTER PROCESS COMMUNICATION MECHANISMS                                                                                                                                                                                                                                                                                                                        | 76                                            |

| 3.7                                           | EVALUATING OPERATING SYSTEM PERFORMANCE                                                                                                                                                                                                                                                                                                                       | 78                                            |

| 3.8                                           | POWER OPTIMIZATION STRATEGIES FOR                                                                                                                                                                                                                                                                                                                             | 79                                            |

|                                               | PROCESSES                                                                                                                                                                                                                                                                                                                                                     |                                               |

|                                               | PROCESSES<br>UNIT IV HARDWARE ACCELERATES & NETWORK                                                                                                                                                                                                                                                                                                           | S                                             |

| 4.1                                           |                                                                                                                                                                                                                                                                                                                                                               | <b>S</b><br>82                                |

| 4.1                                           | UNIT IV HARDWARE ACCELERATES & NETWORK                                                                                                                                                                                                                                                                                                                        |                                               |

| -                                             | UNIT IV HARDWARE ACCELERATES & NETWORK ACCELERATORS                                                                                                                                                                                                                                                                                                           | 82                                            |

| 4.2                                           | UNIT IV HARDWARE ACCELERATES & NETWORK         ACCELERATORS         ACCELERATED SYSTEM DESIGN                                                                                                                                                                                                                                                                 | 82<br>83                                      |

| 4.2<br>4.3                                    | UNIT IV HARDWARE ACCELERATES & NETWORK         ACCELERATORS       ACCELERATED SYSTEM DESIGN         DISTRIBUTED EMBEDDED ARCHITECTURE       ACCELERATED SYSTEM DESIGN                                                                                                                                                                                         | 82<br>83<br>85<br>88                          |

| 4.2<br>4.3<br>4.4                             | UNIT IV HARDWARE ACCELERATES & NETWORK         ACCELERATORS       ACCELERATED SYSTEM DESIGN         ACCELERATED SYSTEM DESIGN       DISTRIBUTED EMBEDDED ARCHITECTURE         NETWORKS FOR EMBEDDED SYSTEMS       ACCELERATED SYSTEMS                                                                                                                         | 82<br>83<br>85<br>88<br>91                    |

| 4.2<br>4.3<br>4.4<br>4.5                      | UNIT IV HARDWARE ACCELERATES & NETWORK         ACCELERATORS       ACCELERATED SYSTEM DESIGN         DISTRIBUTED EMBEDDED ARCHITECTURE       NETWORKS FOR EMBEDDED SYSTEMS         NETWORK BASED DESIGN       ACCELERATED SYSTEM                                                                                                                               | 82<br>83<br>85<br>88                          |

| 4.2<br>4.3<br>4.4<br>4.5                      | UNIT IV HARDWARE ACCELERATES & NETWORK         ACCELERATORS       ACCELERATED SYSTEM DESIGN         ACCELERATED SYSTEM DESIGN       DISTRIBUTED EMBEDDED ARCHITECTURE         NETWORKS FOR EMBEDDED SYSTEMS       NETWORK BASED DESIGN         INTERNET ENABLED SYSTEMS       INTERNET ENABLED SYSTEMS                                                        | 82<br>83<br>85<br>88<br>91                    |

| 4.2<br>4.3<br>4.4<br>4.5                      | UNIT IV HARDWARE ACCELERATES & NETWORK         ACCELERATORS       ACCELERATED SYSTEM DESIGN         ACCELERATED SYSTEM DESIGN       DISTRIBUTED EMBEDDED ARCHITECTURE         NETWORKS FOR EMBEDDED SYSTEMS       NETWORK BASED DESIGN         INTERNET ENABLED SYSTEMS       INTERNET ENABLED SYSTEMS                                                        | 82<br>83<br>85<br>88<br>91                    |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6               | UNIT IV HARDWARE ACCELERATES & NETWORK         ACCELERATORS                                                                                                                                                                                                                                                                                                   | 82<br>83<br>85<br>88<br>91<br>93              |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>5.1        | UNIT IV HARDWARE ACCELERATES & NETWORK         ACCELERATORS       ACCELERATED SYSTEM DESIGN         ACCELERATED SYSTEM DESIGN       DISTRIBUTED EMBEDDED ARCHITECTURE         NETWORKS FOR EMBEDDED SYSTEMS       NETWORK BASED DESIGN         INTERNET ENABLED SYSTEMS       UNIT V CASE STUDY         HARDWARE AND SOFTWARE CO-DESIGN       I               | 82<br>83<br>85<br>88<br>91<br>93<br>97        |

| 4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>5.1<br>5.2 | UNIT IV HARDWARE ACCELERATES & NETWORK         ACCELERATORS       ACCELERATED SYSTEM DESIGN         ACCELERATED SYSTEM DESIGN       DISTRIBUTED EMBEDDED ARCHITECTURE         NETWORKS FOR EMBEDDED SYSTEMS       NETWORK BASED DESIGN         INTERNET ENABLED SYSTEMS       UNIT V CASE STUDY         HARDWARE AND SOFTWARE CO-DESIGN       DATA COMPRESSOR | 82<br>83<br>85<br>88<br>91<br>93<br>97<br>100 |

| 5.5 | SET-TOP-BOX                                   | 108 |

|-----|-----------------------------------------------|-----|

| 5.6 | SYSTEM-ON-SILICON                             | 108 |

| 5.7 | FOSS TOOLS FOR EMBEDDED SYSTEM<br>DEVELOPMENT | 109 |

|     | APPENDICES                                    |     |

| А   | GLOSARY                                       | 110 |

| В   | QUESTION BANK                                 | 115 |

| С   | UNIVERSITY QUESTION                           | 171 |

## EE 8691 EMBEDDED AND REAL TIME SYSTEMS L T P C 3 0 0 3

## **UNIT I INTRODUCTION TO EMBEDDED COMPUTING 9**

Complex systems and microprocessors - Design example: Model train controller -Embedded system design process - Formalism for system design - Instruction sets Preliminaries – ARM Processor – CPU: Programming input and output – Supervisor mode, exception and traps - Coprocessor - Memory system mechanism - CPU performance - CPU power consumption.

## **UNIT II COMPUTING PLATFORM AND DESIGN ANALYSIS 9**

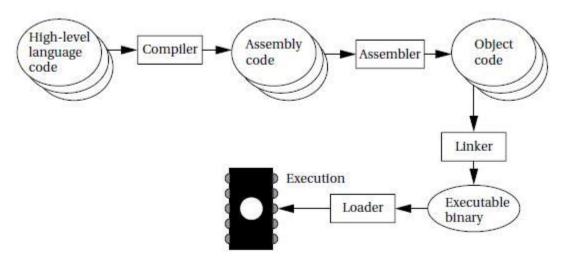

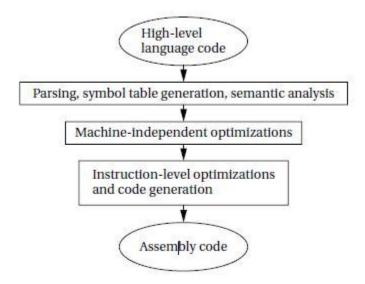

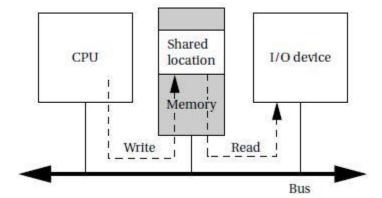

CPU buses – Memory devices – I/O devices – Component interfacing – Design with microprocessors – Development and Debugging – Program design – Model of programs - Assembly and Linking - Basic compilation techniques - Analysis and optimization of execution time, power, energy, program size – Program validation and testing.

#### **UNIT III PROCESS AND OPERATING SYSTEMS 9**

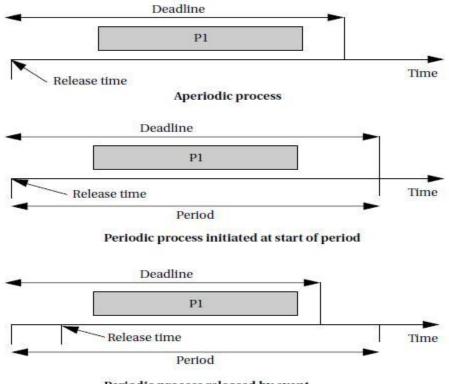

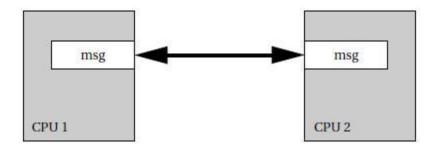

Multiple tasks and multi processes – Processes – Context Switching – Operating Systems – Scheduling policies - Multiprocessor – Inter Process Communication mechanisms – Evaluating operating system performance – Power optimization strategies for processes.

## **UNIT IV HARDWARE ACCELERATES & NETWORKS 9**

Accelerators – Accelerated system design – Distributed Embedded Architecture – Networks for Embedded Systems – Network based design – Internet enabled systems. **UNIT V CASE STUDY 9**

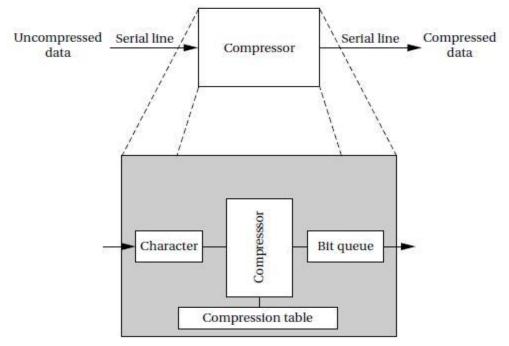

Hardware and software co-design - Data Compressor - Software Modem - Personal Digital Assistants – Set-Top-Box. – System-on-Silicon – FOSS Tools for embedded system development.

#### **TOTAL= 45 PERIODS**

## **TEXT BOOK:**

1) Wayne Wolf, "Computers as Components - Principles of Embedded Computer System Design", Morgan Kaufmann Publisher, 2006.

#### **REFERENCES**:

1) David E-Simon, "An Embedded Software Primer", Pearson Education, 2007. 2) K.V.K.K.Prasad, "Embedded Real-Time Systems: Concepts, Design & Programming", dreamtech press, 2005.

3) Tim Wilmshurst, "An Introduction to the Design of Small Scale Embedded Systems", Pal grave Publisher, 2004.

4) Sriram V Iyer, Pankaj Gupta, "Embedded Real Time Systems Programming", Tata Mc-Graw Hill, 2004.

5) Tammy Noergaard, "Embedded Systems Architecture", Elsevier, 2006.

#### UNIT-1

## **INTRODUCTION TO EMBEDDED COMPUTING**

## COMPLEX SYSTEMS AND MICROPROCESSORS

What is an *embedded computer system*? Loosely defined, it is any device that includes a programmable computer but is not itself intended to be a general-purpose computer. Thus, a PC is not itself an embedded computing system, although PCs are often used to build embedded computing systems. But a fax machine or a clock built from a microprocessor is an embedded computing system.

This means that embedded computing system design is a useful skill for many types of product design. Automobiles, cell phones, and even household appliances make extensive use of microprocessors. Designers in many fields must be able to identify where microprocessors can be used, design a hardware platform with I/O devices that can support the required tasks, and implement software that performs the required processing.

Computer engineering, like mechanical design or thermodynamics, is a fundamental discipline that can be applied in many different domains. But of course, embedded computing system design does not stand alone.

Many of the challenges encountered in the design of an embedded computing system are not computer engineering—for example, they may be mechanical or analog electrical problems. In this book we are primarily interested in the embedded computer itself, so we will concentrate on the hardware and software that enable the desired functions in the final product.

## 1.1 Embedding Computers

Computers have been embedded into applications since the earliest days of computing. One example is the Whirlwind, a computer designed at MIT in the late 1940s and early 1950s. Whirlwind was also the first computer designed to support *real-time* operation and was originally conceived as a mechanism for controlling an aircraft simulator.

Even though it was extremely large physically compared to today's computers (e.g., it contained over 4,000 vacuum tubes), its complete design from components to system was attuned to the needs of real-time embedded computing.

The utility of computers in replacing mechanical or human controllers was evident from the very beginning of the computer era—for example, computers were proposed to control chemical processes in the late 1940s.

A microprocessor is a single-chip CPU. Very large scale integration (VLSI) stet the acronym is the name technology has allowed us to put a complete CPU on a single chip since 1970s, but those CPUs were very simple.

The first microprocessor, the Intel 4004, was designed for an embedded application, namely, a calculator. The calculator was not a general-purpose computer—it merely provided basic arithmetic functions. However, Ted Hoff of Intel realized that a general-purpose computer

EE 8691 EMBEDDDED SYSTEM programmed properly could implement the required function, and that the computer-on-a-chip could then be reprogrammed for use in other products as well.

Since integrated circuit design was (and still is) an expensive and time consuming process, the ability to reuse the hardware design by changing the software was a key breakthrough.

The HP-35 was the first handheld calculator to perform tranndental functions [Whi72]. It was introduced in 1972, so it used several chips to implement the CPU, rather than a single-chip microprocessor.

However, the ability to write programs to perform math rather than having to design digital circuits to perform operations like trigonometric functions was critical to the successful design of the calculator.

Automobile designers started making use of the microprocessor soon after single-chip CPUs became available.

The most important and sophisticated use of microprocessors in automobiles was to control the engine: determining when spark plugs fire, controlling the fuel/air mixture, and so on. There was a trend toward electronics in automobiles in general—electronic devices could be used to replace the mechanical distributor.

But the big push toward microprocessor-based engine control came from two nearly simultaneous developments: The oil shock of the 1970s caused consumers to place much higher value on fuel economy, and fears of pollution resulted in laws restricting automobile engine emissions.

The combination of low fuel consumption and low emissions is very difficult to achieve; to meet these goals without compromising engine performance, automobile manufacturers turned to sophisticated control algorithms that could be implemented only with microprocessors.

Microprocessors come in many different levels of sophistication; they are usually classified by their word size. An 8-bit *microcontroller* is designed for low-cost applications and includes onboard memory and I/O devices; a 16-bit microcontroller is often used for more sophisticated applications that may require either longer word lengths or off-chip I/O and memory; and a 32bit *RISC* microprocessor offers very high performance for computation-intensive applications.

Given the wide variety of microprocessor types available, it should be no surprise that microprocessors are used in many ways. There are many household uses of microprocessors. The typical microwave oven has at least one microprocessor to control oven operation.

Many houses have advanced thermostat systems, which change the temperature level at various times during the day. The modern camera is a prime example of the powerful features that can be added under microprocessor control.

Digital television makes extensive use of embedded processors. In some cases, specialized CPUs are designed to execute important algorithms—an example is the CPU designed for audio

EE 8691 EMBEDDDED SYSTEM processing in the SGS Thomson chip set for DirecTV [Lie98]. This processor is designed to efficiently implement programs for digital audio decoding.

A programmable CPU was used rather than a hardwired unit for two reasons: First, it made the system easier to design and debug; and second, it allowed the possibility of upgrades and using the CPU for other purposes.

A high-end automobile may have 100 microprocessors, but even inexpensive cars today use 40 microprocessors. Some of these microprocessors do very simple things such as detect whether seat belts are in use. Others control critical functions such as the ignition and braking systems.

## BMW 850i brake and stability control system:

The BMW 850i was introduced with a sophisticated system for controlling the wheels of the car. An antilock brake system (ABS) reduces skidding by pumping the brakes.

An automatic stability control (ASC +T) system intervenes with the engine during maneuvering to improve the car's stability. These systems actively control critical systems of the car; as control systems, they require inputs from and output to the automobile.

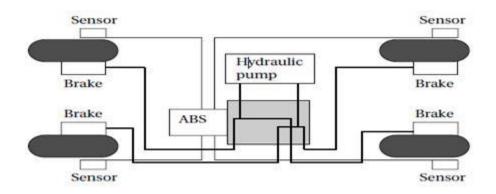

Let's first look at the ABS. The purpose of an ABS is to temporarily release the brake on a wheel when it rotates too slowly—when a wheel stops turning, the car starts skidding and becomes hard to control. It sits between the hydraulic pump, which provides power to the brakes, and the brakes themselves as seen in the following diagram. This hookup allows the ABS system to modulate the brakes in order to keep the wheels from locking.

The ABS system uses sensors on each wheel to measure the speed of the wheel. The wheel speeds are used by the ABS system to determine how to vary the hydraulic fluid pressure to prevent the wheels from skidding.

## Fig 1.1 Antilock brake system (ABS)

The ASC + T system's job is to control the engine power and the brake to improve the car's stability during maneuvers.

The ASC+T controls four different systems: throttle, ignition timing, differential brake, and (on automatic transmission cars) gear shifting.

The ASC + T can be turned off by the driver, which can be important when operating with tire snow chains.

The ABS and ASC+ T must clearly communicate because the ASC + T interacts with the brake system. Since the ABS was introduced several years earlier than the ASC + T, it was important to be able to interface ASC + T to the existing ABS module, as well as to other existing electronic modules.

The engine and control management units include the electronically controlled throttle, digital engine management, and electronic transmission control. The ASC + T control unit has two microprocessors on two printed circuit boards, one of which concentrates on logic-relevant components and the other on performance-specific components.

## 1.1.1 Characteristics of Embedded Computing Applications

Embedded computing is in many ways much more demanding than the sort of programs that you may have written for PCs or workstations. Functionality is important in both general-purpose computing and embedded computing, but embedded applications must meet many other constraints as well.

On the one hand, embedded computing systems have to provide sophisticated functionality:

*Complex algorithms:* The operations performed by the microprocessor may be very sophisticated. For example, the microprocessor that controls an automobile engine must perform complicated filtering functions to optimize the performance of the car while minimizing pollution and fuel utilization.

*User interface:* Microprocessors are frequently used to control complex user interfaces that may include multiple menus and many options. The moving maps in Global Positioning System (GPS) navigation are good examples of sophisticated user interfaces.

To make things more difficult, embedded computing operations must often be performed to meet deadlines:

*Real time:* Many embedded computing systems have to perform in real time— if the data is not ready by a certain deadline, the system breaks. In some cases, failure to meet a deadline is unsafe and can even endanger lives. In other cases, missing a deadline does not create safety problems but does create unhappy customers—missed deadlines in printers, for example, can result in scrambled pages.

*Multirate:* Not only must operations be completed by deadlines, but many embedded computing systems have several real-time activities going on at the same time. They may simultaneously control some operations that run at slow rates and others that run at high rates. Multimedia applications are prime examples of *multirate* behavior. The audio and video portions of a multimedia stream run at very different rates, but they must remain closely synchronized. Failure to meet a deadline on either the audio or video portions spoils the perception of the entire presentation.

Costs of various sorts are also very important:

#### EE 8691

## EMBEDDDED SYSTEM

*Manufacturing cost:* The total cost of building the system is very important in many cases. Manufacturing cost is determined by many factors, including the type of microprocessor used, the amount of memory required, and the types of I/O devices.

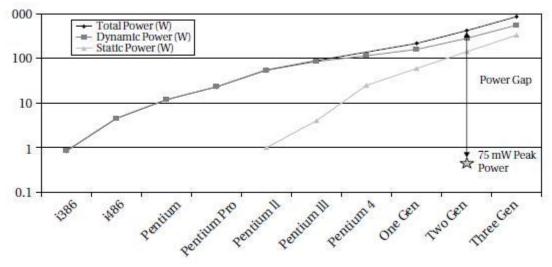

*Power and energy:* Power consumption directly affects the cost of the hardware, since a larger power supply may be necessary. Energy consumption affects battery life, which is important in many applications, as well as heat consumption, which can be important even in desktop applications.

## **1.2 DESIGN EXAMPLE: MODEL TRAIN CONTROLLER**

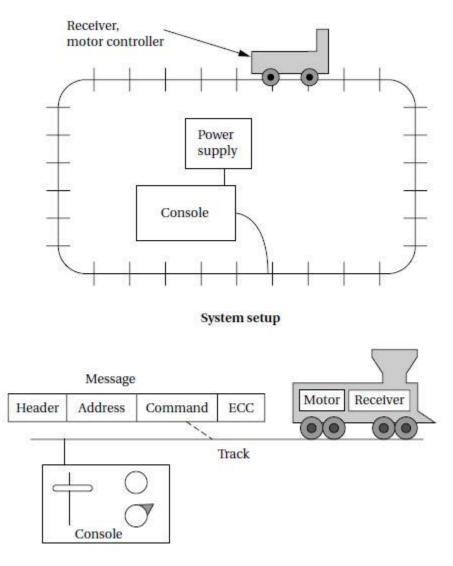

In order to learn how to use UML to model systems, we will specify a simple system, a model train controller, which is illustrated in Figure 1.2. The user sends messages to the train with a control box attached to the tracks.

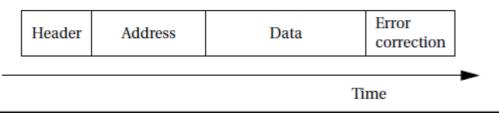

The control box may have familiar controls such as a throttle, emergency stop button, and so on. Since the train receives its electrical power from the two rails of the track, the control box can send signals to the train over the tracks by modulating the power supply voltage. As shown in the figure, the control panel sends packets over the tracks to the receiver on the train.

The train includes analog electronics to sense the bits being transmitted and a control system to set the train motor's speed and direction based on those commands.

Each packet includes an address so that the console can control several trains on the same track; the packet also includes an error correction code (ECC) to guard against transmission errors. This is a one-way communication system the model train cannot send commands back to the user.

We start by analyzing the requirements for the train control system. We will base our system on a real standard developed for model trains. We then develop two specifications: a simple, highlevel specification and then a more detailed specification.

## **1.2.1 Requirements**

Before we can create a system specification, we have to understand the requirements.

Here is a basic set of requirements for the system:

The console shall be able to control up to eight trains on a single track.

The speed of each train shall be controllable by a throttle to at least 63 different levels in each direction (forward and reverse).

There shall be an inertia control that shall allow the user to adjust the responsiveness of the train to commanded changes in speed. Higher inertia means that the train responds more slowly to a change in the throttle, simulating the inertia of a large train. The inertia control will provide at least eight different levels.

There shall be an emergency stop button.

An error detection scheme will be used to transmit messages.

Signaling the train

Fig 1.2 A Model train control system

We can put the requirements into chart format:

| Name                                                                   | Model train controller                                                                                                                                                                         |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose                                                                | Control speed of up to eight model trains                                                                                                                                                      |

| Inputs                                                                 | Throttle, inertia setting, emergency stop, train number                                                                                                                                        |

| Outputs                                                                | Train control signals                                                                                                                                                                          |

| Functions                                                              | Set engine speed based upon inertia settings; respond to<br>emergency stop                                                                                                                     |

| Performance<br>Manufacturing cost<br>Power<br>Physical size and weight | Can update train speed at least 10 times per second<br>\$50<br>10W (plugs into wall)<br>Console should be comfortable for two hands,<br>approximate size of standard keyboard; weight<2 pounds |

We will develop our system using a widely used standard for model train control. We could develop our own train control system from scratch, but basing our system upon a standard has several advantages in this case: It reduces the amount of work we have to do and it allows us to use a wide variety of existing trains and other pieces of equipment.

## <u>1.2.1 DCC</u>

The **Digital Command Control (DCC)** was created by the National Model Railroad Association to support interoperable digitally-controlled model trains.

Hobbyists started building homebrew digital control systems in the 1970s and Marklin developed its own digital control system in the 1980s. DCC was created to provide a standard that could be built by any manufacturer so that hobbyists could mix and match components from multiple vendors.

The DCC standard is given in two documents:

Standard S-9.1, the DCC Electrical Standard, defines how bits are encoded on the rails for transmission.

Standard S-9.2, the DCC Communication Standard, defines the packets that carry information.

Any DCC-conforming device must meet these specifications. DCC also provides several recommended practices. These are not strictly required but they provide some hints to manufacturers and users as to how to best use DCC.

The DCC standard does not specify many aspects of a DCC train system. It doesn't define the control panel, the type of microprocessor used, the programming language to be used, or many other aspects of a real model train system.

The standard concentrates on those aspects of system design that are necessary for interoperability. Over standardization, or specifying elements that do not really need to be standardized, only makes the standard less attractive and harder to implement.

The Electrical Standard deals with voltages and currents on the track. While the electrical engineering aspects of this part of the specification are beyond the scope of the book, we will briefly discuss the data encoding here.

The standard must be carefully designed because the main function of the track is to carry power to the locomotives. The signal encoding system should not interfere with power transmission either to DCC or non-DCC locomotives. A key requirement is that the data signal should not change the DC value of the rails.

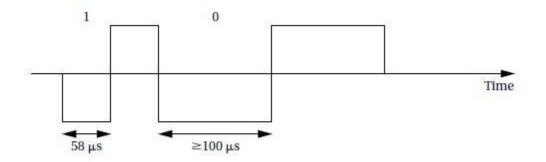

The data signal swings between two voltages around the power supply voltage. As shown in Figure 1.3, bits are encoded in the time between transitions, not by voltage levels. A 0 is at least 100 ms while a 1 is nominally 58ms.

The durations of the high (above nominal voltage) and low (below nominal voltage) parts of a bit are equal to keep the DC value constant. The specification also gives the allowable variations in bit times that a conforming DCC receiver must be able to tolerate.

The standard also describes other electrical properties of the system, such as allowable transition times for signals.

The DCC Communication Standard describes how bits are combined into packets and the meaning of some important packets.

Some packet types are left undefined in the standard but typical uses are given in Recommended Practices documents. We can write the basic packet format as a regular expression:

$$PSA(sD) + E \tag{1.1}$$

Fig1.3 Bit encoding in DCC.

In this regular expression:

*P* is the preamble, which is a sequence of at least 10 1 bits. The command station should send at least 14 of these 1 bits, some of which may be corrupted during transmission.

*S* is the packet start bit. It is a 0 bit.

*A* is an address data byte that gives the address of the unit, with the most significant bit of the address transmitted first. An address is eight bits long. The addresses 00000000, 11111110, and 11111111 are reserved.

*s* is the data byte start bit, which, like the packet start bit, is a 0.

D is the data byte, which includes eight bits. A data byte may contain an address, instruction, data, or error correction information.

E is a packet end bit, which is a 1 bit.

A packet includes one or more data byte start bit/data byte combinations. Note that the address data byte is a specific type of data byte.

A *baseline packet* is the minimum packet that must be accepted by all DCC implementations. More complex packets are given in a Recommended Practice document.

A baseline packet has three data bytes: an address data byte that gives the intended receiver of the packet; the instruction data byte provides a basic instruction; and an error correction data byte is used to detect and correct transmission errors.

The instruction data byte carries several pieces of information. Bits 0-3 provide a 4-bit speed value. Bit 4 has an additional speed bit, which is interpreted as the least significant speed bit. Bit 5 gives direction, with 1 for forward and 0 for reverse. Bits 7–8 are set at 01 to indicate that this instruction provides speed and direction.

The error correction data byte is the bitwise exclusive OR of the address and instruction data bytes.

The standard says that the command unit should send packets frequently since a packet may be corrupted. Packets should be separated by at least 5 ms.

## **<u>1.2.2 Conceptual Specification</u>**

Digital Command Control specifies some important aspects of the system, particularly those that allow equipment to interoperate. But DCC deliberately does not specify everything about a model train control system. We need to round out our specification with details that complement the DCC spec.

## EMBEDDDED SYSTEM

A conceptual specification allows us to understand the system a little better. We will use the experience gained by writing the conceptual specification to help us write a detailed specification to be given to a system architect. This specification does not correspond to what any commercial DCC controllers do, but it is simple enough to allow us to cover some basic concepts in system design.

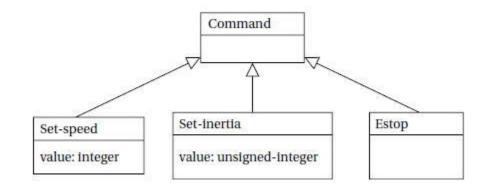

A train control system turns *commands* into *packets*. A command comes from the command unit while a packet is transmitted over the rails.

Commands and packets may not be generated in a 1-to-1 ratio. In fact, the DCC standard says that command units should resend packets in case a packet is dropped during transmission.

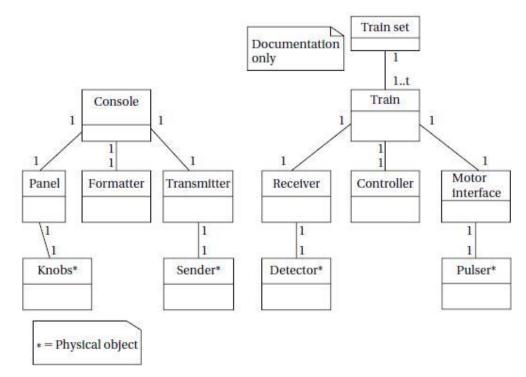

We now need to model the train control system itself. There are clearly two major subsystems: the command unit and the train-board component as shown in Figure 1.4. Each of these subsystems has its own internal structure.

The basic relationship between them is illustrated in Figure 1.5. This figure shows a UML *collaboration diagram*; we could have used another type of figure, such as a class or object diagram, but we wanted to emphasize the transmit/receive relationship between these major subsystems. The command unit and receiver are each represented by objects; the command unit sends a sequence of packets to the train's receiver, as illustrated by the arrow.

The notation on the arrow provides both the type of message sent and its sequence in a flow of messages; since the console sends all the messages, we have numbered the arrow's messages as 1..n. Those messages are of course carried over the track.

Since the track is not a computer component and is purely passive, it does not appear in the diagram. However, it would be perfectly legitimate to model the track in the collaboration diagram, and in some situations it may be wise to model such nontraditional components in the specification diagrams. For example, if we are worried about what happens when the track breaks, modeling the tracks would help us identify failure modes and possible recovery mechanisms.

Fig 1.4 Class diagram for the train controller messages.

## Fig 1.5 UML collaboration diagram for major subsystems of the train controller system.

## Fig 1.6 A UML class diagram for the train controller showing the composition of the subsystems.

Let's break down the command unit and receiver into their major components. The console needs to perform three functions: read the state of the front panel on the command unit, format messages, and transmit messages. The train receiver must also perform three major functions: receive the message, interpret the message (taking into account the current speed, inertia setting, etc.),and actually control the motor. In this case, let's use a class diagram to represent the design; we could also use an object diagram if we wished. The UML class diagram is shown in Figure 1.6. It shows the console class using three classes, one for each of its major components. These classes must define some behaviors, but for the moment we will concentrate on the basic characteristics of these classes:

The *Console* class describes the command unit's front panel, which contains the analog knobs and hardware to interface to the digital parts of the system.

The *Formatter* class includes behaviors that know how to read the panel knobs and creates a bit stream for the required message.

The *Transmitter* class interfaces to analog electronics to send the message along the track.

There will be one instance of the *Console* class and one instance of each of the component classes, as shown by the numeric values at each end of the relationship links. We have also shown some special classes that represent analog components, ending the name of each with an asterisk:

*Knobs*\* describes the actual analog knobs, buttons, and levers on the control panel.

*Sender*\* describes the analog electronics that send bits along the track.

Likewise, the Train makes use of three other classes that define its components:

The Receiver class knows how to turn the analog signals on the track into digital form.

The *Controller* class includes behaviors that interpret the commands and figures out how to control the motor.

The Motor interface class defines how to generate the analog signals required to control the motor.

We define two classes to represent analog components:

Detector\* detects analog signals on the track and converts them into digital form.

Pulser\* turns digital commands into the analog signals required to control the motor speed.

We have also defined a special class, *Train set*, to help us remember that the system can handle multiple trains. The values on the relationship edge show that one train set can have *t* trains. We would not actually implement the train set class, but it does serve as useful documentation of the existence of multiple receivers.

## **1.3 THE EMBEDDED SYSTEM DESIGN PROCESS**

This section provides an overview of the embedded system design process aimed at two objectives. First, it will give us an introduction to the various steps in embedded system design before we delve into them in more detail. Second, it will allow us to consider the design *methodology* itself. A design methodology is important for three reasons.

First, it allows us to keep a scorecard on a design to ensure that we have done everything we need to do, such as optimizing *performance* or performing functional tests.

Second, it allows us to develop computer-aided design tools. Developing a single program that takes in a concept for an embedded system and emits a completed design would be a daunting task, but by first breaking the process into manageable steps, we can work on automating (or at least semi automating) the steps one at a time.

Third, a design methodology makes it much easier for members of a design team to communicate. By defining the overall process, team members can more easily understand what they are supposed to do, what they should receive from other team members at certain times,

and what they are to hand off when they complete their assigned steps. Since most embedded systems are designed by teams, coordination is perhaps the most important role of a well-defined design methodology.

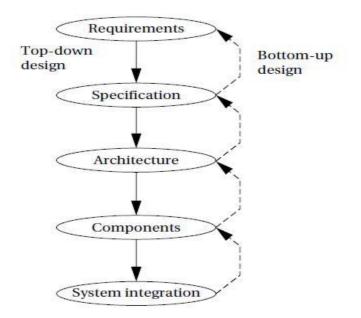

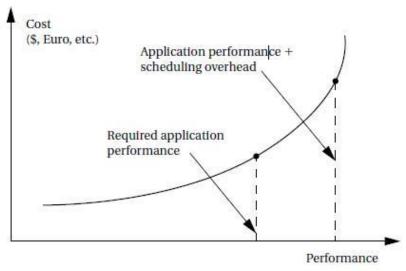

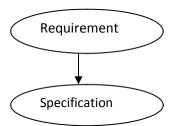

Figure 1.7 summarizes the major steps in the embedded system design process. In this topdown view, we start with the system *requirements*. In the next step, *specification*, we create a more detailed description of what we want.

But the specification states only how the system behaves, not how it is built. The details of the system's internals begin to take shape when we develop the architecture, which gives the system structure in terms of large components.

Once we know the components we need, we can design those components, including both software modules and any specialized hardware we need. Based on those components, we can finally build a complete system.

Fig 1.7 Major levels of abstraction in the design process.

In this section we will consider design from the *top-down*—we will begin with the most abstract description of the system and conclude with concrete details. The alternative is a **bottom-up** view in which we start with components to build a system.

Bottom-up design steps are shown in the figure as dashed-line arrows. We need bottom-up design because we do not have perfect insight into how later stages of the design process will turn out. Decisions at one stage of design are based upon estimates of what will happen later: How fast can we make a particular function run? How much memory will we need? How much system bus capacity do we need? If our estimates are inadequate, we may have to backtrack and

EE 8691 EMBEDDDED SYSTEM amend our original decisions to take the new facts into account. In general, the less experience we have with the design of similar systems, the more we will have to rely on bottom-up design information to help us refine the system.

But the steps in the design process are only one axis along which we can view embedded system design. We also need to consider the major goals of the design:

Manufacturing cost; Performance (both overall speed and deadlines); and Power consumption.

We must also consider the tasks we need to perform at every step in the design process. At each step in the design, we add detail:

We must *analyze* the design at each step to determine how we can meet the specifications. We must then *refine* the design to add detail. We must verify the design to ensure that it still meets all system goals, such as cost, speed, and so on.

## **<u>1.3.1 Requirements</u>**

Clearly, before we design a system, we must know what we are designing. The initial stages of the design process capture this information for use in creating the architecture and components.

We generally proceed in two phases: First, we gather an informal description from the customers known as requirements, and we refine the requirements into a specification that contains enough information to begin designing the system architecture.

Separating out requirements analysis and specification is often necessary because of the large gap between what the customers can describe about the system they want and what the architects need to design the system.

Consumers of embedded systems are usually not themselves embedded system designers or even product designers. Their understanding of the system is based on how they envision users' interactions with the system. They may have unrealistic expectations as to what can be done within their budgets; and they may also express their desires in a language very different from system architects' jargon.

Capturing a consistent set of requirements from the customer and then massaging those requirements into a more formal specification is a structured way to manage the process of translating from the consumer's language to the designer's.

Requirements may be *functional* or *nonfunctional*.Wemust of course capture the basic functions of the embedded system, but functional description is often not sufficient.Typical nonfunctional requirements include:

#### EE 8691

## EMBEDDDED SYSTEM

*Performance:* The speed of the system is often a major consideration both for the usability of the system and for its ultimate cost. As we have noted, performance may be a combination of soft performance metrics such as approximate time to perform a user-level function and hard deadlines by which a particular operation must be completed.

*Cost:* The target cost or purchase price for the system is almost always a consideration. Cost typically has two major components: *manufacturing cost* includes the cost of components and assembly; *nonrecurring engineering* (NRE) costs include the personnel and other costs of designing the system.

*Physical size and weight:* The physical aspects of the final system can vary greatly depending upon the application. An industrial control system for an assembly line may be designed to fit into a standard-size rack with no strict limitations on weight. A handheld device typically has tight requirements on both size and weight that can ripple through the entire system design.

*Power consumption:* Power, of course, is important in battery-powered systems and is often important in other applications as well. Power can be specified in the requirements stage in terms of battery life—the customer is unlikely to be able to describe the allowable wattage.

Validating a set of requirements is ultimately a psychological task since it requires understanding both what people want and how they communicate those needs. One goodway to refine at least the user interface portion of a system's requirements is to build a *mock-up*.

The mock-up may use canned data to simulate functionality in a restricted demonstration, and it may be executed on a PC or a workstation. But it should give the customer a good idea of how the system will be used and how the user can react to it. Physical, nonfunctional models of devices can also give customers a better idea of characteristics such as size and weight.

Name Purpose Inputs Outputs Functions Performance Manufacturing cost Power Physical size and weight

## Fig 1.8 Sample requirements form.

Requirements analysis for big systems can be complex and time consuming. However, capturing a relatively small amount of information in a clear, simple format is a good start toward understanding system requirements.

To introduce the discipline of requirements analysis as part of system design, we will use a simple requirements methodology.

Figure 1.8 shows a sample *requirements form* that can be filled out at the start of the project. We can use the form as a checklist in considering the basic characteristics of the system.

Let's consider the entries in the form:

- *Name:* This is simple but helpful. Giving a name to the project not only simplifies talking about it to other people but can also crystallize the purpose of the machine.

- *Purpose:* This should be a brief one- or two-line description of what the system is supposed to do. If you can't describe the essence of your system in one or two lines, chances are that you don't understand it well enough.

- *Inputs and outputs:* These two entries are more complex than they seem. The inputs and outputs to the system encompass a wealth of detail:

- Types of data: Analog electronic signals? Digital data? Mechanical inputs?

- *Data characteristics:* Periodically arriving data, such as digital audio samples? Occasional user inputs? How many bits per data element?

- Types of I/O devices: Buttons? Analog/digital converters? Video displays?

*Functions:* This is a more detailed description of what the system does. A good way to approach this is to work from the inputs to the outputs: When the system receives an input, what does it do? How do user interface inputs affect these functions? How do different functions interact?

*Performance:* Many embedded computing systems spend at least some time controlling physical devices or processing data coming from the physical world. In most of these cases, the computations must be performed within a certain time frame. It is essential that the performance requirements be identified early since they must be carefully measured during implementation to ensure that the system works properly.

*Manufacturing cost:* This includes primarily the cost of the hardware components. Even if you don't know exactly how much you can afford to spend on system components, you should have some idea of the eventual cost range. Cost has a substantial influence on architecture: A machine that is meant to sell at \$10 most likely has a very different internal structure than a \$100 system.

*Power:* Similarly, you may have only a rough idea of how much power the system can consume, but a little information can go a long way. Typically, the most important decision is whether the machine will be battery powered or plugged into the wall. Battery-powered machines must be much more careful about how they spend energy.

*Physical size and weight:* You should give some indication of the physical size of the system to help guide certain architectural decisions. A desktop machine has much more flexibility in the components used than, for example, a lapel mounted voice recorder.

#### EE 8691

## **1.4 FORMALISMS FOR SYSTEM DESIGN:**

Visual language that can be used to capture all these design tasks: the *Unified Modeling Language (UML)*. UML was designed to be useful at many levels of abstraction in the design process. UML is useful because it encourages design by successive refinement and progressively adding detail to the design, rather than rethinking the design at each new level of abstraction.

UML is an *object-oriented* modeling language. We will see precisely what we mean by an object in just a moment, but object-oriented design emphasizes two concepts of importance:

It encourages the design to be described as a number of interacting objects, rather than a few large monolithic blocks of code.

At least some of those object will correspond to real pieces of software or hardware in the system. We can also use UML to model the outside world that interacts with our system, in which case the objects may correspond to people or other machines. It is sometimes important to implement something we think of at a high level as a single object using several distinct pieces of code or to otherwise break up the object correspondence in the implementation However, thinking of the design in terms of actual objects helps us understand the natural structure of the system. Object-oriented (often abbreviated OO) specification can be seen in two complementary ways:

Object-oriented specification allows a system to be described in a way that closely models real-world objects and their interactions.

Object-oriented specification provides a basic set of primitives that can be used to describe systems with particular attributes, irrespective of the relationships of those systems' components to real-world objects.

Both views are useful. At a minimum, object-oriented specification is a set of linguistic mechanisms. In many cases, it is useful to describe a system in terms of real-world analogs. However, performance, cost, and so on may dictate that we change the specification to be different in some ways from the real-world elements we are trying to model and implement. In this case, the object-oriented specification mechanisms are still useful.

A specification language may not be executable. But both object-oriented specification and programming languages provide similar basic methods for structuring large systems.

Unified Modeling Language (UML)—the acronym is the name is a large language, and covering all of it is beyond the scope of this book. In this section, we introduce only a few basic concepts. In later chapters, as we need a few more UML concepts, we introduce them to the basic modeling elements introduced here.

Because UML is so rich, there are many graphical elements in a UML diagram. It is important to be careful to use the correct drawing to describe something for instance; UML distinguishes between arrows with open and filled-in arrowheads, and solid and broken lines. As you become more familiar with the language, uses of the graphical primitives will become more natural to you.

#### EE 8691

We also won't take a strict object-oriented approach. We may not always use objects for certain elements of a design—in some cases, such as when taking particular aspects of the implementation into account, it may make sense to use another design style. However, object-oriented design is widely applicable, and no designer can consider himself or herself design literate without understanding it.

## **<u>1.4.1 Structural Description</u>**:

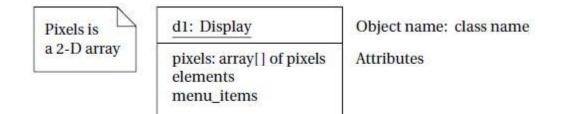

By *structural description*, we mean the basic components of the system; we will learn how to describe how these components act in the next section. The principal component of an object-oriented design is, naturally enough, the *object*. An object includes a set of *attributes* that define its internal state.

When implemented in a programming language, these attributes usually become variables or constants held in a data structure. In some cases, we will add the type of the attribute after the attribute name for clarity, but we do not always have to specify a type for an attribute. An object describing a display (such as a CRT screen) is shown in UML notation in Figure 1.8 a).

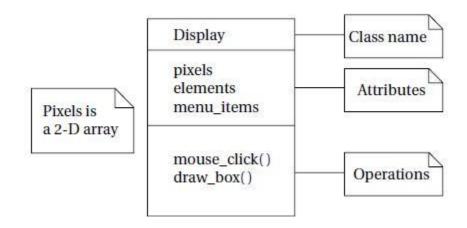

The text in the folded-corner page icon is a *note*; it does not correspond to an object in the system and only serves as a comment. The attribute is, in this case, an array of pixels that holds the contents of the display. The object is identified in two ways: It has a unique name, and it is a member of a *class*. The name is underlined to show that this is a description of an object and not of a class.

A class is a form of type definition—all objects derived from the same class have the same characteristics, although their attributes may have different values. A class defines the attributes that an object may have. It also defines the *operations* that determine how the object interacts with the rest of the world. In a programming language, the operations would become pieces of code used to manipulate the object.

The UML description of the *Display* class is shown in Figure 1.8 b). The class has the name that we saw used in the d1 object since d1 is an instance of class *Display*.

The *Display* class defines the *pixels* attribute seen in the object; remember that when we instantiate the class an object, that object will have its own memory so that different objects of the same class have their own values for the attributes. Other classes can examine and modify class attributes; if we have to do something more complex than use the attribute directly, we define a behavior to perform that function.

A class defines both the *interface* for a particular type of object and that object's *implementation*. When we use an object, we do not directly manipulate its attributes—we can only read or modify the object's state through the operations that define the interface to the object.

As long as we do not change the behavior of the object seen at the interface, we can change the implementation as much as we want. This lets us improve the system by, for example, speeding up an operation or reducing the amount of memory required without requiring changes to anything else that uses the object.

Fig 1.8 a) An object in UML notation

Fig 1.8 b) A class in UML notation

Clearly, the choice of an interface is a very important decision in object-oriented design. The proper interface must provide ways to access the object's state (since we cannot directly see the attributes) as well as ways to update the state.

We need to make the object's interface general enough so that we can make full use of its capabilities. However, excessive generality often makes the object large and slow. Big, complex interfaces also make the class definition difficult for designers to understand and use properly.

There are several types of *relationships* that can exist between objects and classes:

■*Association* occurs between objects that communicate with each other but have no ownership relationship between them.

Aggregation describes a complex object made of smaller objects.

•*Composition* is a type of aggregation in which the owner does not allow access to the component objects.

Generalization allows us to define one class in terms of another.

## **<u>1.4.2 Behavioral Description</u>:**

We have to specify the behavior of the system as well as its structure. One way to specify the behavior of an operation is a *state machine*.

These state machines will not rely on the operation of a clock, as in hardware; rather, changes from one state to another are triggered by the occurrence of *events*.

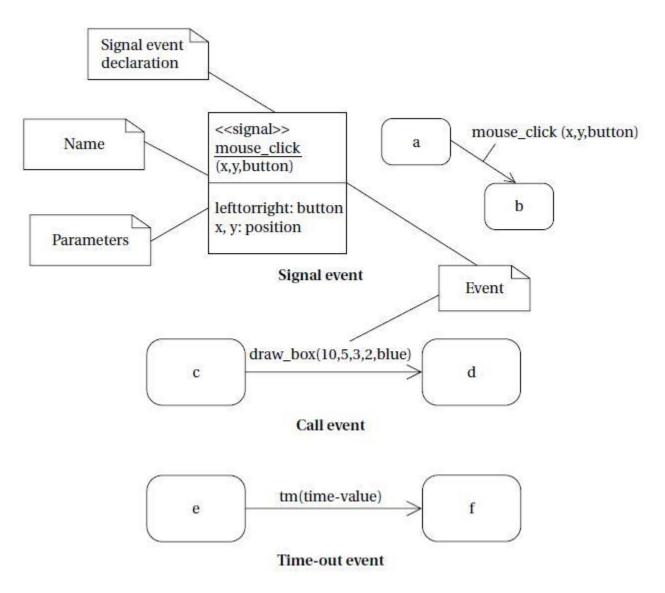

Fig 1.8 c) Signal, call, and time-out events in UML.

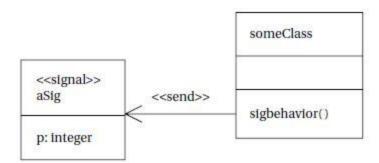

An event is some type of action. The event may originate outside the system, such as a user pressing a button. It may also originate inside, such as when one routine finishes its computation and passes the result on to another routine. We will concentrate on the following three types of events defined by UML, as illustrated in Figure 1.8 c):

A *signal* is an asynchronous occurrence. It is defined in UML by an object that is labeled as a *<<signal>>*. The object in the diagram serves as a declaration of the event's existence. Because it is an object, a signal may have parameters that are passed to the signal's receiver.

A *call event* follows the model of a procedure call in a programming language.

■A *time-out event* causes the machine to leave a state after a certain amount of time. The label *tm(time-value)* on the edge gives the amount of time after which the transition occurs. A time-out is generally implemented with an external timer. This notation simplifies the specification and allows us to defer implementation details about the time-out mechanism.

## **1.5 INSTRUCTION SETS PRELIMINERIS:**

## **1.5.1 Computer Architecture Taxonomy**

Before we delve into the details of microprocessor instruction sets, it is helpful to develop some basic terminology. We do so by reviewing taxonomy of the basic ways we can organize a computer.

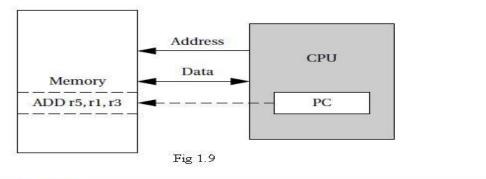

A block diagram for one type of computer is shown in Figure 1.9. The computing system consists of a *central processing unit (CPU)* and a *memory*.

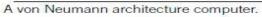

The memory holds both data and instructions, and can be read or written when given an address. A computer whose memory holds both data and instructions is known as a *von Neumann* machine.

The CPU has several internal *registers* that store values used internally. One of those registers is the *program counter (PC)*, which holds the address in memory of an instruction. The CPU fetches the instruction from memory, decodes the instruction, and executes it.

The program counter does not directly determine what the machine does next, but only indirectly by pointing to an instruction in memory. By changing only the instructions, we can change what the CPU does. It is this separation of the instruction memory from the CPU that distinguishes a stored-program computer from a general finite-state machine.

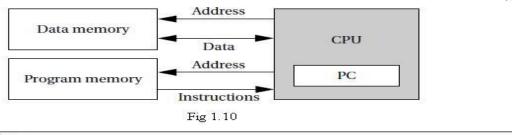

An alternative to the von Neumann style of organizing computers is the **Harvard architecture**, which is nearly as old as the von Neumann architecture. As shown in Figure 1.10, a Harvard machine has separate memories for data and program.

The program counter points to program memory, not data memory. As a result, it is harder to write self-modifying programs (programs that write data values, and then use those values as instructions) on Harvard machines.

A Harvard architecture.

Harvard architectures are widely used today for one very simple reason—the separation of program and data memories provides higher performance for digital signal processing.

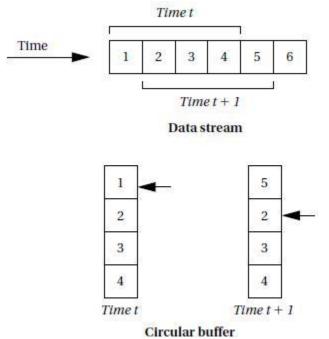

Processing signals in real-time places great strains on the data access system in two ways: First, large amounts of data flow through the CPU; and second, that data must be processed at precise intervals, not just when the CPU gets around to it. Data sets that arrive continuously and periodically are called *streaming data*.

Having two memories with separate ports provides higher memory bandwidth; not making data and memory compete for the same port also makes it easier to move the data at the proper times. DSPs constitute a large fraction of all microprocessors sold today, and most of them are Harvard architectures.

A single example shows the importance of DSP: Most of the telephone calls in the world go through at least two DSPs, one at each end of the phone call.

Another axis along which we can organize computer architectures relates to their instructions and how they are executed. Many early computer architectures were what is known today as *complex instruction set computers (CISC)*. These machines provided a variety of instructions that may perform very complex tasks, such as string searching; they also generally used a number of different instruction formats of varying lengths.

One of the advances in the development of high-performance microprocessors was the concept of *reduced instruction set computers (RISC)*. These computers tended to provide somewhat fewer and simpler instructions.

The instructions were also chosen so that they could be efficiently executed in *pipelined* processors. Early RISC designs substantially outperformed CISC designs of the period. As it turns out, we can use RISC techniques to efficiently execute at least a common subset of CISC instruction sets, so the performance gap between RISC-like and CISC-like instruction sets has narrowed somewhat.

Beyond the basic RISC/CISC characterization, we can classify computers by several characteristics of their instruction sets. The instruction set of the computer defines the interface between software modules and the underlying hardware; the instructions define what the hardware will do under certain circumstances. Instructions can have a variety of characteristics, including:

Fixed versus variable length.

Addressing modes.

Numbers of operands.

Types of operations supported.

The set of registers available for use by programs is called the *programming model*, also known as the *programmer model*. (The CPU has many other registers that are used for internal operations and are unavailable to programmers.)

There may be several different implementations of architecture. In fact, the architecture definition serves to define those characteristics that must be true of all implementations and what may vary from implementation to implementation.

Different CPUs may offer different clock speeds, different cache configurations, changes to the bus or interrupt lines, and many other changes that can make one model of CPU more attractive than another for any given application.

#### **1.5.2 Assembly Language**

Figure 1.11 shows a fragment of ARM assembly code to remind us of the basic features of assembly languages. Assembly languages usually share the same basic features:

- $\Box \overline{A}$ 뛷j $\Box \overline{A}$  One instruction appears per line.

- $\Box \overline{A}$  岩 $\overline{J} \Box \overline{A}$  *Labels*, which give names to memory locations, start in the first column.

$\Box \overline{A}$  泪 $i \Box \overline{A}$  Instructions must start in the second column or after to distinguish them from labels.

$\Box \overline{A}$  当 $\overline{J} \Box \overline{A}$  Comments run from some designated comment character (; in the case of ARM) to the end of the line.

- Assembly language follows this relatively structured form to make it easy for the *assembler* to parse the program and to consider most aspects of the program line by line. (It should be remembered that early assemblers were written in assembly language to fit in a very small amount of memory.

- Those early restrictions have carried into modern assembly languages by tradition.) Figure 2.4 shows the format of an ARM data processing instruction such as an ADD.

ADDGT r0, r3, #5

For the instruction the *cond* field would be set according to the GT condition (1100), the *opcode* field would be set to the binary code for the ADD instruction (0100), the first *operand* register Rn would be set to 3 to represent r3, the destination register Rd would be set to 0 for r0, and the *operand 2* field would be set to the immediate value of 5.

Assemblers must also provide some *pseudo-ops* to help programmers create complete assembly language programs.

An example of a pseudo-op is one that allows data values to be loaded into memory locations. These allow constants, for example, to be set into memory.

An example of a memory allocation pseudo-op for ARM is shown in Figure 2.5.TheARM % pseudo-op allocates a block of memory of the size specified by the operand and initializes those locations to zero.

| label1 | ADR r4,c     |                   |

|--------|--------------|-------------------|

|        | LDR r0,[r4]  | ; a comment       |

|        | ADR r4,d     |                   |

|        | LDR r1,[r4]  |                   |

|        | SUB r0,r0,r1 | ; another comment |

|        |              |                   |

An example of ARM assembly language.

Fig 1.11

| Rd Format determined by X bit |

|-------------------------------|

| nediate                       |

| nediate                       |

|                               |

| 0                             |

| 0                             |

| 0                             |

| Rm                            |

|                               |

| 3 0                           |

| 1 Rm                          |

|                               |

|                               |

| % 10                          |

|                               |

| 1                             |

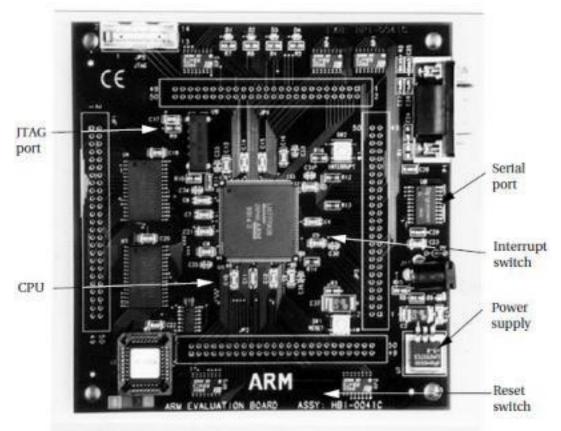

## **1.6 ARM PROCSSOR:**

In this section, we concentrate on the ARM processor. ARM is actually a family of RISC architectures that have been developed over many years.

ARM does not manufacture its own VLSI devices; rather, it licenses its architecture to companies who either manufacture the CPU itself or integrate the ARM processor into a larger system.

The textual description of instructions, as opposed to their binary representation, is called an assembly language.

ARM instructions are written one per line, starting after the first column. Comments begin with a semicolon and continue to the end of the line. A label, which gives a name to a memory location, comes at the beginning of the line, starting in the first column. Here is an example:

LDR r0, [r8]; a comment

label ADD r4,r0,r1

## **1.6.1 Processor and Memory Organization:**

Different versions of the ARM architecture are identified by different numbers. ARM7 is a von Neumann architecture machine, while ARM9 uses Harvard architecture.

However, this difference is invisible to the assembly language programmer, except for possible performance differences.

The ARM architecture supports two basic types of data:

The standard ARM word is 32 bits long.

The word may be divided into four 8-bit bytes.

ARM7 allows addresses up to 32 bits long. An address refers to a byte, not a word. Therefore, the word 0 in the ARM address space is at location 0, the word 1 is at 4, the word 2 is at 8, and so on. (As a result, the PC is incremented by 4 in the absence of a branch.)

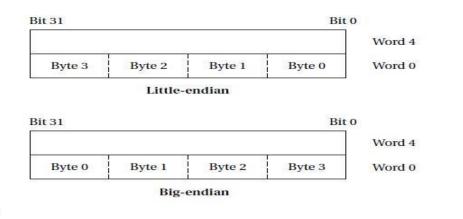

The ARM processor can be configured at power-up to address the bytes in a word in either *little-endian* mode (with the lowest-order byte residing in the low-order bits of the word) or *big-endian* mode (the lowest-order byte stored in the highest bits of the word), as illustrated in Figure 1.14 [Coh81]. General purpose computers have sophisticated instruction sets.

Some of this sophistication is required simply to provide the functionality of a general computer, while other aspects of instruction sets may be provided to increase performance, reduce code size, or otherwise improve program characteristics.

#### Fig 1.14

Byte organizations within an ARM word.

## EE 8691 **1.6.2 Data Operations:**

Arithmetic and logical operations in C are performed in variables. Variables are implemented as memory locations. Therefore, to be able to write instructions to perform C expressions and assignments, we must consider both arithmetic and logical instructions as well as instructions for reading and writing memory.

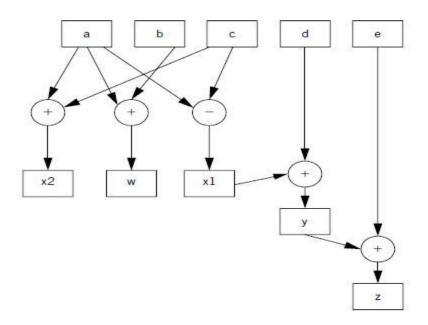

Figure 1.15 shows a sample fragment of C code with data declarations and several assignment statements. The variables a, b, c, x, y, and z all become data locations in memory. In most cases data are kept relatively separate from instructions in the program's memory image.

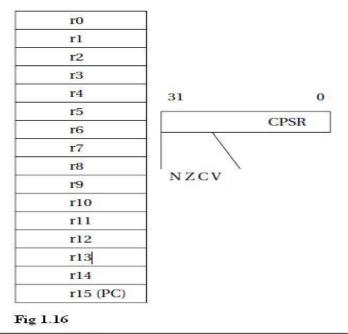

In the ARM processor, arithmetic and logical operations cannot be performed directly on memory locations. While some processors allow such operations to directly reference main memory, ARM is a *load-store architecture*—data operands must first be loaded into the CPU and then stored back to main memory to save the results. Figure 2.8 shows the registers in the basic ARM programming model. ARM has 16 general-purpose registers, r0 through r15. Except for r15, they are identical—any operation that can be done on one of them can be done on the other one also.

The r15 register has the same capabilities as the other registers, but it is also used as the program counter. The program counter should of course not be overwritten for use in data operations. However, giving the PC the properties of a general-purpose register allows the program counter value to be used as an operand in computations, which can make certain programming tasks easier. The other important basic register in the programming model is the *current program status register (CPSR)*.

This register is set automatically during every arithmetic, logical, or shifting operation. The top four bits of the CPSR hold the following useful information about the results of that arithmetic/logical operation:

The negative (N) bit is set when the result is negative in two's-complement arithmetic.

The zero (Z) bit is set when every bit of the result is zero.

The carry (C) bit is set when there is a carry out of the operation.

The overflow(V) bit is set when an arithmetic operation results in an overflow.

```

int a, b, c, x, y, z;

= (a+b)-c;

y=a*(b+c);

z=(a << 2) | (b & 15);

```

## Figs 1.15 A C fragment with data operations.

These bits can be used to check easily the results of an arithmetic operation. However, if a chain of arithmetic or logical operations is performed and the intermediate states of the CPSR bits are important, then they must be checked at each step since the next operation changes the CPSR values.

The basic ARM programming model.

The basic form of a data instruction is simple:

ADD r0,r1,r2

This instruction sets register r0 to the sum of the values stored in r1 and r2. In addition to specifying registers as sources for operands, instructions may also provide *immediate operands*, which encode a constant value directly in the instruction. For example,

## ADD r0,r1,#2 sets r0 to r1+2.

The major data operations are summarized in Figure 1.17. The arithmetic operations perform addition and subtraction; the with-carry versions include the current value of the carry bit in the computation.

RSB performs a subtraction with the order of the two operands reversed, so that RSB r0, r1, r2 sets r0 to be r2\_r1. The bit-wise logical operations perform logical AND, OR, and XOR operations (the exclusive or is called EOR).

The BIC instruction stands for bit clear: BIC r0, r1, r2 sets r0 to r1 and not r2. This instruction uses the second source operand as a mask: Where a bit in the mask is 1, the corresponding bit in the first source operand is cleared.

The MUL instruction multiplies two values, but with some restrictions: No operand may be an immediate, and the two source operands must be different registers.

The MLA instruction performs a multiply-accumulate operation, particularly useful in matrix operations and signal processing. The instruction MLA r0, r1, r2, r3

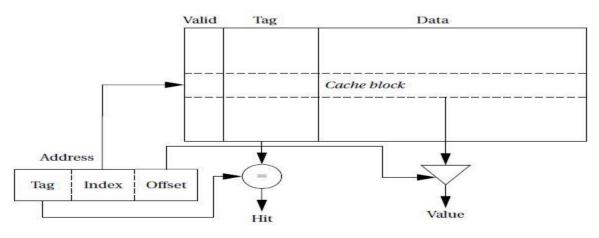

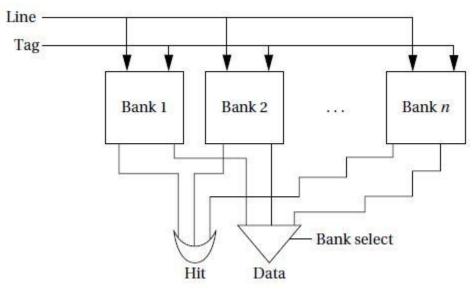

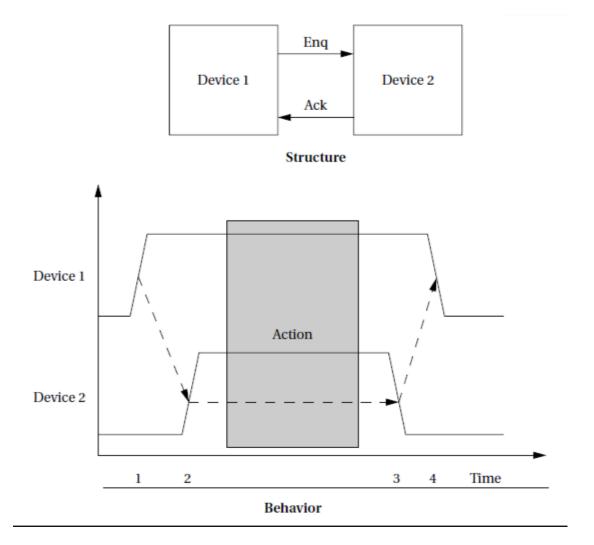

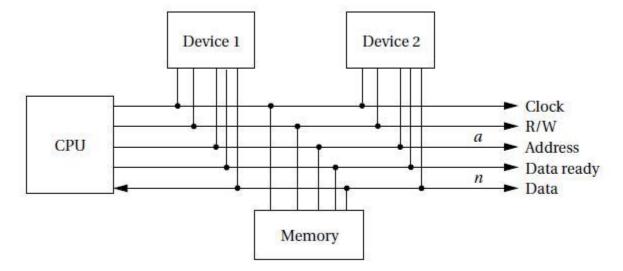

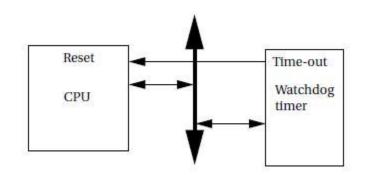

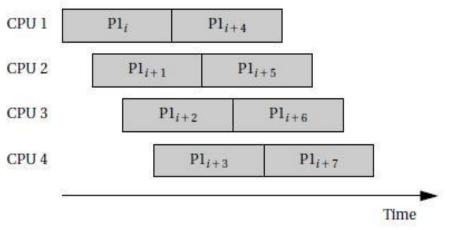

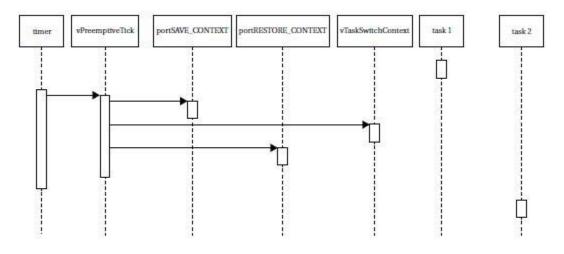

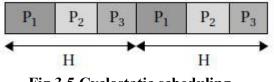

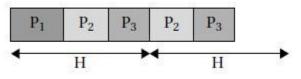

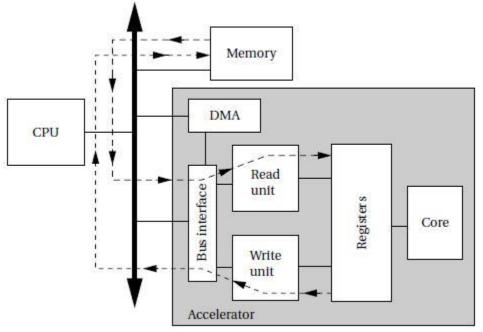

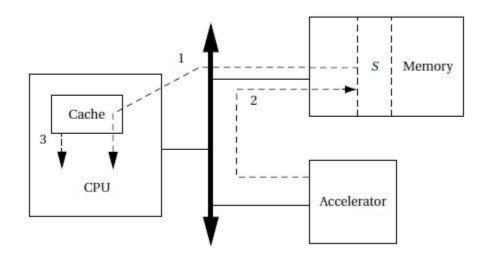

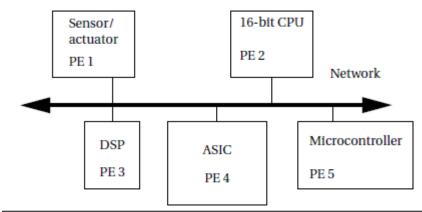

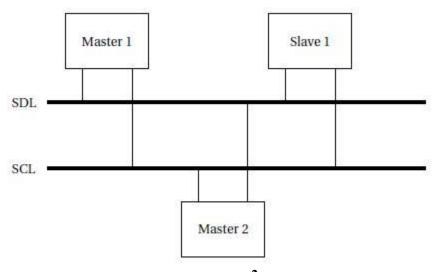

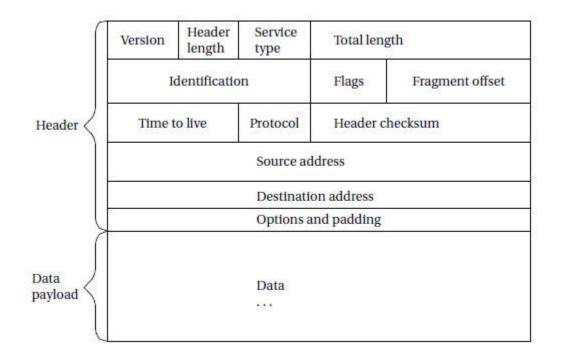

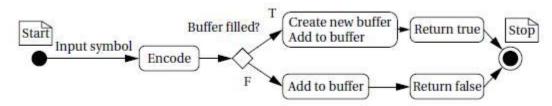

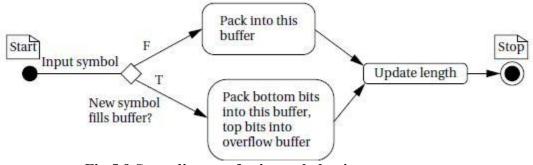

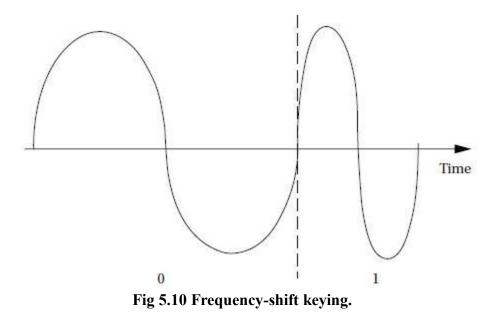

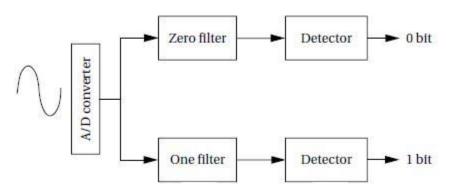

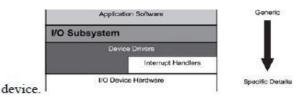

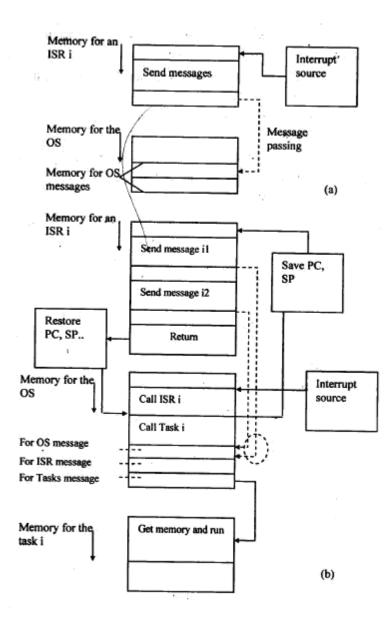

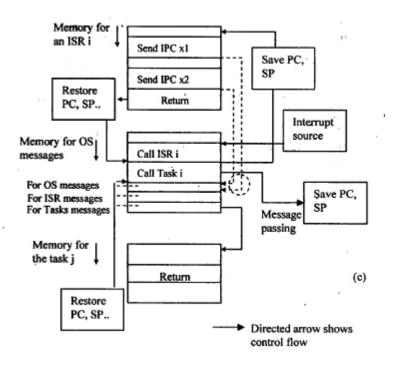

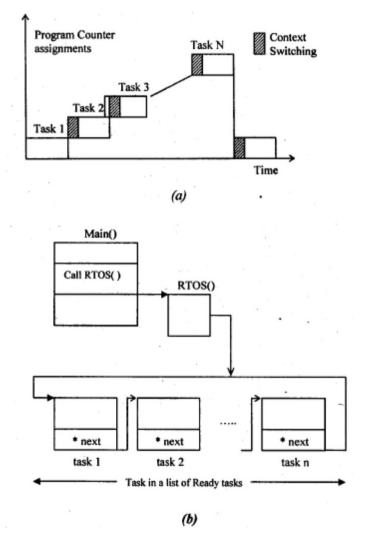

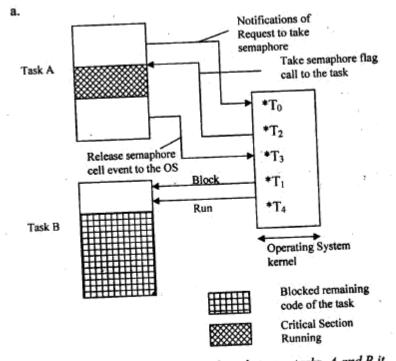

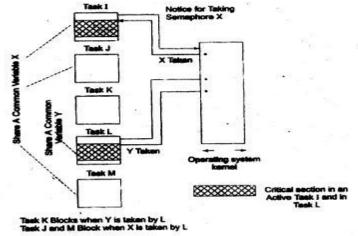

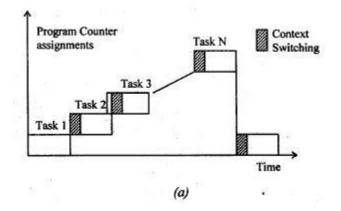

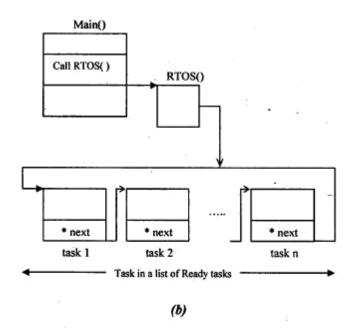

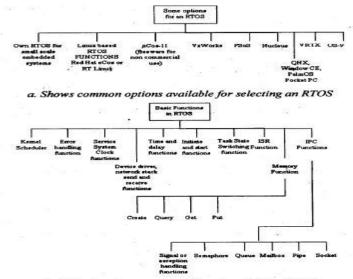

Sets r0 to the value r1\*r2+r3.