# PRATHYUSHA ENGINEERING COLLEGE

Poonamallee – Tiruvallur Road, Chennai – 602025.

## CS8491 Computer Architecture

(Anna University – 2017 Regulation)

Prepared by Ms.R.Kannamma, AP in CSE, PEC

#### <u>UNIT – I</u>

#### UNIT I BASIC STRUCTURE OF A COMPUTER SYSTEM

Functional Units – Basic Operational Concepts – Performance – Instructions: Language of the Computer – Operations, Operands – Instruction representation – Logical operations – decision making – MIPS Addressing.

9

## **COMPONENTS OF A COMPUTER SYSTEM**

#### BASIC STRUCTURE OF COMPUTER

#### COMPUTER

A Computer is a machine which accepts input information in the digitized form, processes the input according to a set of stored instructions and gives an output in a form understandable by user.

## PROGRAM AND DATA

The set of stored instructions according which input are processed by computer are called programs and input and output information is called data.

## **TYPES OF COMPUTER**

Computers are classified according to size, cost, power of the processor, and type of usage. Personal computers are most

common computers and Super computers are most powerful computers.

Some of types of computer are

- Personal computers

- Notebook computers

- ➢ Workstations

- Enterprise systems and Servers

- > Mainframes

- > Supercomputers

## I. HARDWARE PARTS OF THE COMPUTER SYSTEM:

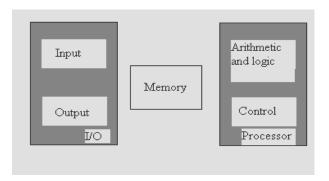

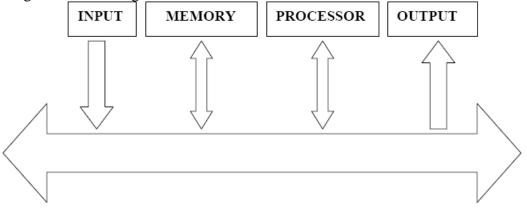

- A computer consists of five functionally independent main parts

- 1. Input

- 2. Output

- 3. ALŪ

- 4. Control Unit

- 5. Memory

The operation of a computer can be summarized as follows

- $\checkmark$  The computer accepts programs and the data through an input and stores them in the memory.

- $\checkmark$  The stored data are processed by the arithmetic and logic unit under program control.

- $\checkmark$  The processed data is delivered through the output unit.

- $\checkmark$  All above activities are directed by control unit

## <u>Input unit</u>

- > The computer accepts coded information through input unit. The input can be from human operators, electromechanical devices such as keyboards or from other computer over communication lines.

- Examples of input devices are

- ✓ Keyboard, joysticks, trackballs and mouse are used as graphic input devices in conjunction with display.

- $\checkmark$  Microphones can be used to capture audio input.

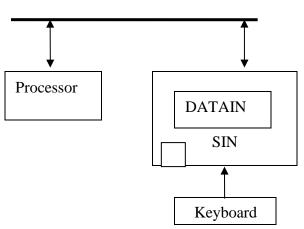

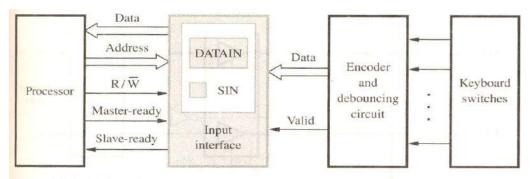

#### Keyboard

- It is a common input device.

- Whenever a key is pressed, the corresponding letter or digit is automatically translated into its corresponding binary code and transmitted over cable to the memory of the computer.

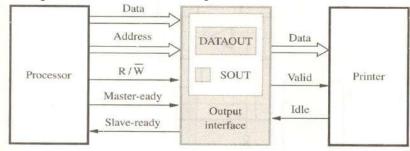

#### <u>Output unit</u>

- The function of output unit is to produce processed result to the outside world in human understandable form.

- Examples of output devices are Printer, Graphical display.

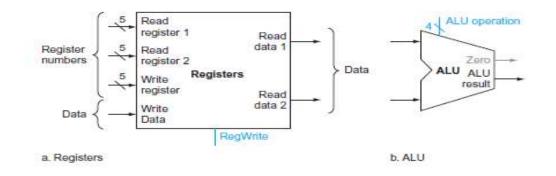

## Arithmetic and logic unit

Arithmetic and logic unit (ALU) and control unit together form a processor.

Actual execution of most computer operations takes place in arithmetic and logic unit of the processor. <u>Example:</u>

Suppose two numbers located in the memory are to be added. They are brought into the processor, and the actual addition is carried out by the ALU.

## **Registers:**

- ▶ Registers are high speed storage elements available in the processor.

- Each register can store one word of data.

- > When operands are brought into the processor for any operation, they are stored in the registers.

- Accessing data from register is faster than that of the memory.

<u>Control unit</u> Control unit coordinates the operation of memory, arithmetic and logic unit, input unit, and output unit. Control unit sends control signals to other units and senses their states.

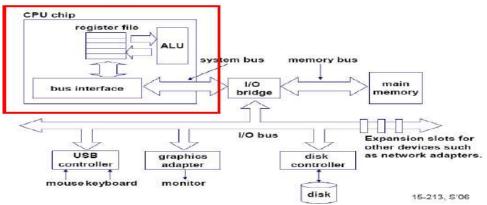

**Central processor unit**(**CPU**) : Also called processor. The active part of the computer, which contains the datapath and control and which adds numbers, tests numbers, signals I/O devices to activate, and so on.

Datapath: The component of the processor that performs arithmetic operations.

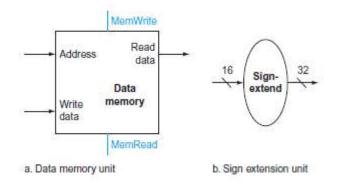

#### Memory unit

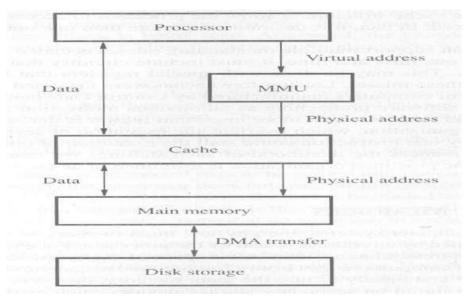

The storage area in which programs are kept when they are running and that contains the data needed by the running programs. Memory is classified into primary and secondary storage.

## Primary storage

- ➢ It also called main memory.

- > It operates at high speed and it is expensive.

- > It is Volatile memory (which loses its data when the power is turned off)

- > It is directly accessed by CPU to store and retrieve information.

- > It is made up of large number of semiconductor storage cells, each capable of storing one bit of information.

- > Programs must reside in the primary memory during execution.

- ► RAM:

- ✓ It stands for random access memory. Memory in which any location can be reached in a short and fixed amount of time by specifying its address is called random-access memory.

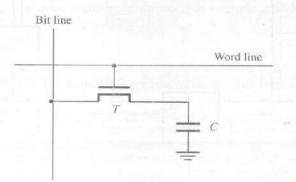

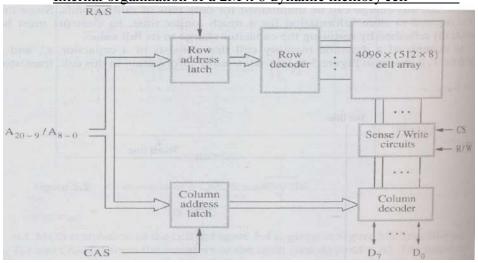

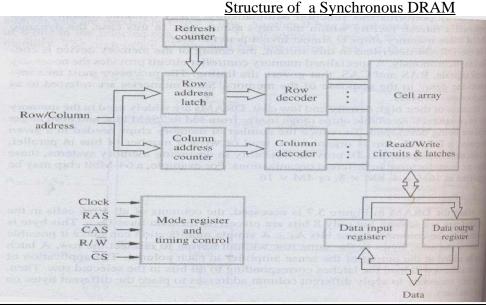

- > Two types are static DRAM (SRAM) and Dynamic RAM(DRAM).

- The memory is where the programs are kept when they are running; it also contains the data needed by the running programs. The memory is built from DRAM chips. *DRAM* stands for dynamic random access memory.

- static random access memory (SRAM) Also memory built as an integrated circuit, but faster and less dense than DRAM

- > Cache Memory

- ✓ They are small and fast RAM units.

- $\checkmark$  They are tightly coupled with the processor.

- $\checkmark$  They are often contained on the same integrated circuits(IC) chip to achieve high performance.

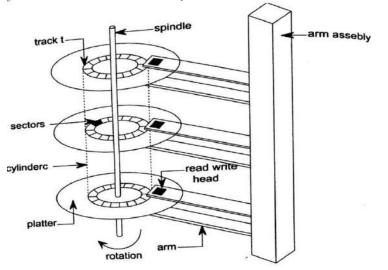

#### Secondary memory

- $\succ$  It is slow in speed.

- ➢ It is cheaper than primary memory.

- ➢ Its capacity is high.

- ▶ It is used to store information that is not accessed frequently.

- > Various secondary devices are magnetic tapes and disks, optical disks (CD-ROMs), floppy etc.

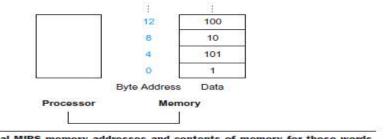

## MEMORY ORGANIZATION

The memory is organized as collection of words. Each word is referred by an address 0 to M

BIT (BINARY DIGIT): The memory contain large number of storage cells, each capable of storing 0 or 1 is called a BIT

**WORD:** cells are grouped together in a fixed size called word. This facilitates reading and writing the content of one word (n bits) in single basic operation instead of reading and writing one bit for each operation. Each word is associated with a distinct address that identifies word location. A given word is accessed by specifying its address. **Wordlength** :The number of bits in each word is called as Wordlength

Addresses: These are the numbers that identified each location / word in memory

Byte: 8 Bits of memory is called Byte

#### **Byte Addressable:**

The memory is said to be byte addressable if every byte has separate address.Modern Processors use Byte addressing

Byte addressing within a word is represented in two ways

#### i. Big Endian Addressing

## ii. Little Endian Addressing

| Big-endian Arrang | ement             |                   |                   |                   | Little-endian Arrangement |   |                   |                   |                   |                   |

|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|---|-------------------|-------------------|-------------------|-------------------|

| Word address      |                   | Byt               | e addres          | SS                | Word address              | B | yte addı          | ess               |                   |                   |

| 0                 | 0                 | 1                 | 2                 | 3                 | 0                         |   | 3                 | 2                 | 1                 | 0                 |

| 4                 | 4                 | 5                 | 6                 | 7                 | 4                         |   | 7                 | 6                 | 5                 | 4                 |

|                   |                   | •                 |                   |                   |                           |   |                   | •                 |                   |                   |

|                   |                   | •                 |                   |                   |                           |   |                   | •                 |                   |                   |

|                   |                   | •                 |                   |                   |                           |   |                   | •                 |                   |                   |

|                   |                   |                   |                   |                   | 2 <sup>k</sup> -4         | ŀ | 2 <sup>k</sup> -1 | 2 <sup>k</sup> -2 | 2 <sup>k</sup> -3 | 2 <sup>k</sup> -4 |

| 2 <sup>k</sup> -4 | 2 <sup>k</sup> -4 | 2 <sup>k</sup> -3 | 2 <sup>k</sup> -2 | 2 <sup>k</sup> -1 |                           |   |                   |                   |                   |                   |

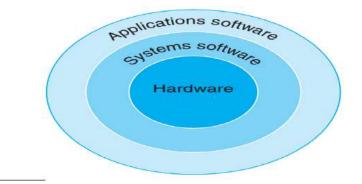

## II. Software:

Software can be divided into two categories. 1. System software and 2. Application software. **System software:** System software are the program that runs and control the hardware units of the system. System software gets installed when the operating system is installed on the computer. It includes programs for compiler, linker and loader etc.

**Application software:** Application software runs over the system software. These software are installed according to the requirements of the user. Example: C, C++, Java, Ms-word etc.

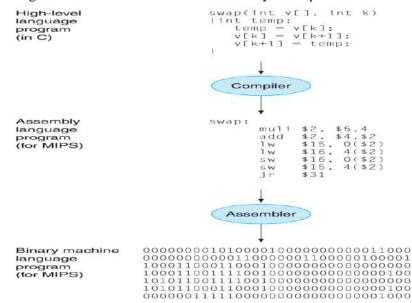

**Compiler:** A Program that translates high-level language statements into assembly language statements. It takes entire program as input. The program need not be compiled everytime. The errors are displayed after the entire program is checked.

**Interpreter:** It takes single instruction as input. Everytime high level languages are converted in to Low level language. The errors are displayed after every instruction interpreted.

Assembler: A program that translates a symbolic version of instructions(Assembly language program) into the binary version.

Assembly language: A symbolic representation of machine instructions. Instructions arewritten using Mnemonics.

Machine language: A binary representation of machine instructions.

**High level Programming Language:** A portable language such as C, C++, Java or Visual Basicthat is composed of words and algebraic notation that can be translated by a compiler into assembly language.

For example:

A compiler enables a programmer to write this high-level language expression:

A + B

The compiler would compile it into this assembly language statement:

add A,B

The assembler would translate this statement into the binary instruction that tells the computer to add the two numbers A and B:

1000110010100000

## TECHNOLOGY USED IN COMPUTER

The technology that have been used in computers are changing constantly over time and it is given below.

| Year | Technology used in computers         | Relative performance/unit cost |

|------|--------------------------------------|--------------------------------|

| 1951 | Vacuum tube                          | 1                              |

| 1965 | Transistor                           | 35                             |

| 1975 | Integrated circuit                   | 900                            |

| 1995 | Very large-scale integrated circuit  | 2,400,000                      |

| 2013 | Ultra large-scale integrated circuit | 250,000,000,000                |

- <u>Vacuum Tube</u>is the electronic component used in I<sup>st</sup> generation computer. An electronic component that consists of a hollow glass tube about 5 to 10 cm long from which as much air hasbeen removed as possible and which uses an electron beam to transfer data.

- <u>**Transistor**</u> is the semiconductor device used in II<sup>nd</sup> generation computer. It is an on/off switch controlled by an electric signal. This will reduce the physical size and power dissipation of the computer and increase the performance.

- **Integrated** Circuit(IC) combined dozens to hundreds of transistors into a single chip. This will further reduce the physical size, power dissipation and increase the performance.

- <u>Very large scale integrated (VLSI) circuit:</u>A device containing hundreds of thousands to millions of transistors.

- <u>Ultra large-scale integration (ULSI)</u> is the process of integrating or embedding millions of transistors on a single silicon semiconductor microchip.

Moore's Law: The number of transistors is a chip is doubled in every 18 to 24 months.

Growth of DRAM capacity

Moore's law resulted from a prediction of such growth in IC capacity made by Gordon Moore, one of the founders of Intel during the 1960s.

The growth of Dram capacity quadrupled for every 3 years from 1977 to 1995 and in recent years the rate of increase has slowdown and approximately doubling every 2 or 3 years.

| Year | - | Chip Size |

|------|---|-----------|

| 1977 | - | 16 K      |

| 1980 | - | 64 K      |

| 1983 | - | 256 K     |

| 1986 | - | 1 M       |

| 1989 | - | 4M     |

|------|---|--------|

| 1992 | - | 16 M   |

| 1996 | - | 64 M   |

| 1998 | - | 128 M  |

| 2000 | - | 256 M  |

| 2004 | - | 512 M  |

| 2007 | - | 1 Gbit |

|      |   |        |

## Growth of Transistor in processors.

|      | L |             |   |                  |

|------|---|-------------|---|------------------|

| Year |   | Processor   | - | No of Transistor |

| 1978 | - | 8086        | - | 20,000           |

| 1982 | - | 80286       | - | 100,000          |

| 1985 | - | 80386       | - | 200,000          |

| 1989 | - | 80486       | - | 1000,000         |

| 1993 | - | Pentium     | - | $5 \ge 10^6$     |

| 2001 | - | Pentium IV  | - | $20 \ge 10^6$    |

| 2005 | - | Core 2 dual | - | $200 \ge 10^6$   |

|      |   |             |   |                  |

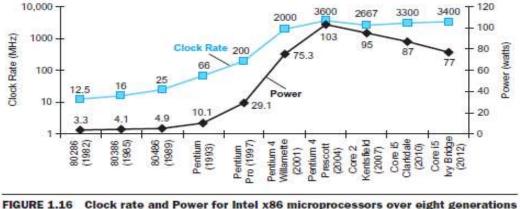

#### **POWER WALL**

Both clock rate and power increased rapidly fordecades, and then flattened off recently. For CMOS, the primary source of energy consumption is so-called dynamic energy—that is, energy that is consumed when transistors switch states from 0 to 1 and vice versa. The dynamic energy depends on the capacitive loading of each transistor and the voltage applied:

#### The increase in clock rate and power of eight generations of Intel microprocessors over 30 years.

and 25 years. The Pentium 4 made a dramatic jump in clock rate and power but less so in performance. The Perscott thermal problems led to the abandonment of the Pentium 4 line. The Core 2 line reverts to a simpler pipeline with lower clock rates and multiple processors per chip. The Core i5 pipelines follow in its footsteps.

The dynamic energy depends on the capacitive loading of each transistor and the voltage applied  $Energy \propto Capacitive \ load \times Voltage^2$

The energy of a single transition is then

Energy  $\propto 1/2 \times Capacitive load \times Voltage^2$

The dynamic power dissipation depends on the capacitive loading of each transistor, the voltage applied and the frequency that the transistor is switched.

Power = Capacitive Load x Voltage<sup>2</sup> x Frequency switched.

Frequency switched is a function of the clock rate. The capacitive load per transistor is a function of both the number of transistors connected to an output (called the *fanout*) and the technology, which determines the capacitance of

both wires and transistors.

#### The above figure shows how could clock rates grow by a factor of 1000 while power grew by only a factor of 30?

Energy and thus power can be reduced by lowering the voltage, which occurred with each new generation of technology, and power is a function of the voltage squared. Typically, the voltage was reduced about15% per generation. In 20 years, voltages have gone from 5 V to 1 V, which is whythe increase in power is only 30 times.

#### PERFORMANCE MEASURE

Performance of a computer can be measured by speed with which it can execute the program. Response time and Throughput are the two factors to measure the performance.

**Response time** Also called **execution time**. The total time required for the computer to complete a task, including disk accesses, memory accesses, I/O activities, operating system overhead, CPU execution time, and so on.

**Throughput** Also called **bandwidth**. Another measure of performance, it is the number of tasks completed per unit time.

Speed of the computer is affected by

- ➢ Hardware design

- Machine language instruction of the computer.

Compiler, which translates high-level language into machine language.

For best performance, it is necessary to design hardware, machine instruction set and compiler in a coordinated way.

## I. <u>RELATIVE PERFORMANCE</u>

$$Performance_{X} = \frac{1}{Execution time_{X}}$$

This means that for two computers X and Y, if the performance of X is greater than the performance of Y, we have

$\begin{array}{l} \mbox{Performance}_{\chi} > \mbox{Performance}_{\chi} \\ \hline \hline 1 \\ \hline Execution \mbox{time}_{\chi} \\ \mbox{Execution \mbox{time}}_{\chi} > \mbox{Execution \mbox{time}}_{\chi} \end{array}$

That is, the execution time on Y is longer than that on X, if X is faster than Y.

In discussing a computer design, we often want to relate the performance of two different computers quantitatively. We will use the phrase "X is *n* times faster than Y"—or equivalently "X is *n* times as fast as Y"—to mean

$$\frac{\text{Performance}_{X}}{\text{Performance}_{Y}} = n$$

If X is *n* times as fast as Y, then the execution time on Y is *n* times as long as it is on X:

$$\frac{\text{Performance}_{\chi}}{\text{Performance}_{\chi}} = \frac{\text{Execution time}_{\chi}}{\text{Execution time}_{\chi}} = n$$

#### **Relative Performance**

If computer A runs a program in 10 seconds and computer B runs the same program in 15 seconds, how much faster is A than B?

We know that A is *n* times as fast as B if  $\frac{\text{Performance}_{A}}{\text{Performance}_{A}} = \frac{\text{Execution time}_{B}}{\text{Execution time}_{B}} = n$

$\frac{1}{\text{Performance}_{B}} = \frac{1}{\text{Execution time}_{A}} = n$

Thus the performance ratio is

$$\frac{15}{10} = 1.5$$

and A is therefore 1.5 times as fast as B.

In the above example, we could also say that computer B is 1.5 times *slower than* computer A, since

$\frac{\text{Performance}_{\Lambda}}{\text{Performance}_{B}} = 1.5$

means that

$\frac{\text{Performance}_{A}}{1.5} = \text{Performance}_{B}$

## II. <u>CPU PERFORMANCE AND ITS FACTOR</u>

execution time. A simple formula relates the most basic metrics (clock cycles and clock cycle time) to CPU time:

> CPU execution time for a program = CPU clock cycles for a program × Clock cycle time

Alternatively, because clock rate and clock cycle time are inverses,

$\frac{\text{CPU execution time}}{\text{for a program}} = \frac{\text{CPU clock cycles for a program}}{\text{Clock rate}}$

We can now write this basic performance equation in terms of instruction count (the number of instructions executed by the program), CPI, and clock cycle time: CPU time = Instruction count × CPI × Clock cycle time

or, since the clock rate is the inverse of clock cycle time:

$CPU time = \frac{Instruction \ count \times CPI}{Clock \ rate}$

These formulas are particularly useful because they separate the three key factors that affect performance. We can use these formulas to compare two different implementations or to evaluate a design alternative if we know its impact on these three parameters.

## EXAMPLE IMPROVING PERFORMANCE

Our favorite program runs in 10 seconds on computer A, which has a 2 GHz clock. We are trying to help a computer designer build a computer, B, which will run this program in 6 seconds. The designer has determined that a substantial increase in the clock rate is possible, but this increase will affect the rest of the CPU design, causing computer B to require 1.2 times as many clock cycles as computer A for this program. What clock rate should we tell the designer to target?

Let's first find the number of clock cycles required for the program on A:

$$CPU time_{A} = \frac{CPU clock cycles_{A}}{Clock rate_{A}}$$

$$10 seconds = \frac{CPU clock cycles_{A}}{2 \times 10^{9} \frac{cycles}{second}}$$

CPU clock cycles<sub>A</sub> = 10 seconds  $\times 2 \times 10^9 \frac{\text{cycles}}{\text{second}} = 20 \times 10^9 \text{ cycles}$

CPU time for B can be found using this equation:

$$CPU \text{ time}_{B} = \frac{1.2 \times CPU \text{ clock cycles}_{A}}{Clock \text{ rate}_{B}}$$

$$6 \text{ seconds} = \frac{1.2 \times 20 \times 10^{9} \text{ cycles}}{Clock \text{ rate}_{B}}$$

$$Clock \text{ rate}_{B} = \frac{1.2 \times 20 \times 10^{9} \text{ cycles}}{6 \text{ seconds}} = \frac{0.2 \times 20 \times 10^{9} \text{ cycles}}{\text{second}} = \frac{4 \times 10^{9} \text{ cycles}}{\text{second}} = 4 \text{ GHz}$$

To run the program in 6 seconds, B must have twice the clock rate of A.

## III. INSTRUCTION PERFORMANCE

$CPU \ clock \ cycles = Instructions \ for \ a \ program \times \\ \begin{array}{c} Average \ clock \ cycles \\ per \ instruction \end{array}$

#### **EXAMPLE:**

Suppose we have two implementations of the same instruction set architecture. Computer A has a clock cycle time of 250 ps and a CPI of 2.0 for some program, and computer B has a clock cycle time of 500 ps and a CPI of 1.2 for the same program. Which computer is faster for this program and by how much?

We know that each computer executes the same number of instructions for the program; let's call this number *I*. First, find the number of processor clock cycles for each computer:

CPU clock cycles<sub>A</sub> =  $I \times 2.0$ CPU clock cycles<sub>B</sub> =  $I \times 1.2$

Now we can compute the CPU time for each computer:

$\operatorname{CPU}\operatorname{time}_{A}=\operatorname{CPU}\operatorname{clock}\operatorname{cycles}_{A}\times\operatorname{Clock}\operatorname{cycle}\operatorname{time}$

$= I \times 2.0 \times 250 \text{ ps} = 500 \times I \text{ ps}$

Likewise, for B:

CPU time<sub>B</sub> =  $I \times 1.2 \times 500$  ps =  $600 \times I$  ps

Clearly, computer A is faster. The amount faster is given by the ratio of the execution times:

$\frac{\text{CPU performance}_{\text{A}}}{\text{CPU performance}_{\text{B}}} = \frac{\text{Execution time}_{\text{B}}}{\text{Execution time}_{\text{A}}} = \frac{600 \times I \text{ ps}}{500 \times I \text{ ps}} = 1.2$

We can conclude that computer A is 1.2 times as fast as computer B for this program.

#### The Classic CPU Performance Equation:

We can now write this basic performance equation in terms of instruction count (the number of instructions executed by the program), CPI, and clock cycle time:

CPU time = Instruction count × CPI × Clock cycle time

or, since the clock rate is the inverse of clock cycle time:

CPU time = <u>Instruction count × CPI</u> <u>Clock rate</u>

#### **Example:**

A compiler designer is trying to decide between two code sequences for a particular computer. The hardware designers have supplied the following facts:

|     | CPI for each instruction class |   |   |  |  |

|-----|--------------------------------|---|---|--|--|

|     | ×                              | 8 | C |  |  |

| CPI | 1                              | 2 | 3 |  |  |

For a particular high-level language statement, the compiler writer is considering two code sequences that require the following instruction counts:

|               | Instruction counts for each instruction class |   |            |  |

|---------------|-----------------------------------------------|---|------------|--|

| tode sequence | Α                                             | B | e          |  |

| 1             | 2                                             | 2 | 2          |  |

| 2             | 4                                             | 1 | 1 <b>1</b> |  |

Which code sequence executes the most instructions? Which will be faster? What is the CPI for each sequence?

#### Solution:

Sequence 1 executes 2 + 1 + 2 = 5 instructions. Sequence 2 executes 4 + 1 + 1 = 6 instructions. Therefore, sequence 1 executes fewer instructions. We can use the equation for CPU clock cycles based on instruction count and CPI to find the total number of clock cycles for each sequence.

CPU clock cycles =

$$\sum_{i=1}^{n} (CPI_i \times C_i)$$

This yields

CPU clock cycles<sub>1</sub> =  $(2 \times 1) + (1 \times 2) + (2 \times 3) = 2 + 2 + 6 = 10$  cycles

CPU clock cycles<sub>2</sub> =  $(4 \times 1) + (1 \times 2) + (1 \times 3) = 4 + 2 + 3 = 9$  cycles

So code sequence 2 is faster, even though it executes one extra instruction. Since code sequence 2 takes fewer overall clock cycles but has more instructions, it must have a lower CPI. The CPI values can be computed by

$$\begin{split} \mathrm{CPI} &= \frac{\mathrm{CPU} \ \mathrm{clock} \ \mathrm{cycles}}{\mathrm{Instruction} \ \mathrm{count}} \\ \mathrm{CPI}_{\mathrm{t}} &= \frac{\mathrm{CPU} \ \mathrm{clock} \ \mathrm{cycles}_{\mathrm{t}}}{\mathrm{Instruction} \ \mathrm{count}_{\mathrm{t}}} = \frac{10}{5} = 2.0 \\ \mathrm{CPI}_{\mathrm{2}} &= \frac{\mathrm{CPU} \ \mathrm{clock} \ \mathrm{cycles}_{\mathrm{2}}}{\mathrm{Instruction} \ \mathrm{count}_{\mathrm{2}}} = \frac{9}{6} = 1.5 \end{split}$$

| Components of performance          | Units of measure                               |  |

|------------------------------------|------------------------------------------------|--|

| CPU execution time for a program   | Seconds for the program                        |  |

| Instruction count                  | Instructions executed for the program          |  |

| Clock cycles per instruction (CPI) | Average number of clock cycles per instruction |  |

| Clock cycle time                   | Seconds per clock cycle                        |  |

#### FIGURE 4.2 The basic components of performance and how each is measured.

Designers often obtain CPI by a detailed simulation of an implementation or by using hardware counters, when a CPU is operational. Sometimes it is possible to compute the CPU clock cycles by looking at the different types of instructions and using their individual clock cycle counts. In such cases, the following formula is useful:

CPU clock cycles =

$$\sum_{i=1}^{n} (CPI_i \times C_i)$$

where  $C_i$  is the count of the number of instructions of class *i* executed,  $CPI_i$  is the average number of cycles per instruction for that instruction class, and *n* is the number of instruction classes.

#### PERFORMANCE MEASUREMENT

The computer community adopted the idea of measuring computer performance using benchmark programs. To make comparisons possible, standardized programs must be used. The performance measure is the time it takes a computer to execute a given benchmark.

A nonprofit organization called System Performance Evaluation Corporation (SPEC) measures the performance of the system.

The SPEC rating is computed as follows

Running time on the reference computer

SPEC rating = -----

Running time on the computer under test

Let SPECi be the rating for program i in the suite. The overall SPEC rating for the computer is given by

SPEC rating =

$$\left(\prod_{i=1}^{n} SPEC_i\right)^{\frac{1}{n}}$$

where n is the number of programs in the suite

## **INSTRUCTION IN MIPS**

## **OPERATION AND OPERANDS IN MIPS**

#### Based on operations the MIPS instructions are classified into five groups/Instructions types

- 1. Arithmetic instruction

- 2. Logical Instructions

- 3. Data transfer Instructions

- 4. Conditional Branch Instructions

- 5. Unconditional Jump Instructions

#### 1. Arithmetic instructions(R-Type)

Sub

addi

These Instructions will perform arithmetic operations with register only.

Examples: add for addition of two registers

for subtraction

for adding a constant

#### **Arithmetic Instructions**

| Instruction   | Example               | Meaning          | Comments                |

|---------------|-----------------------|------------------|-------------------------|

| add           | add \$\$1,\$\$2,\$\$3 | \$s1=\$s2+\$s3   | Three register operands |

| subtract      | sub \$s1,\$s2,\$s3    | \$s1=\$s2 - \$s3 | Three register operands |

| add immediate | addi \$s1,\$s2,20     | \$s1=\$s2 + 20   | Used to add constants   |

#### Example 1:

C code for the following instruction:

f = (g + h) - (i + j);

➤ f, ..., j in \$s0, ..., \$s4

Compiled MIPS code: add \$t0, \$s1, \$s2 add \$t1, \$s3, \$s4 sub \$s0, \$t0, \$t1

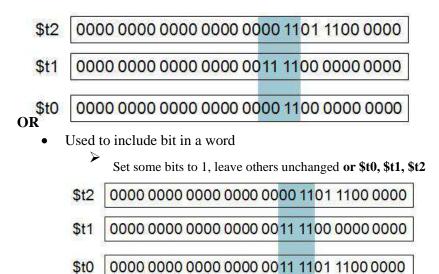

## 2. Logical Instructions ( LOGICAL OPERATIONS)

These Instruction will perform logic operations and shift operations with register only.

Shift Instruction moves all the bits in a word to the left or right, filling the emptied bits with 0s. The

shamt field in the R-format. It stands for shift amount and is used in shift instructions.

## **Logical Instructions**

| Instruction | Example | Meaning           | Comments                            |

|-------------|---------|-------------------|-------------------------------------|

| and         | and     | \$s1 =\$s2 & \$s3 | Three register operands; bit-by-bit |

|                        | \$s1,\$s2,\$s3       |                          | AND                                        |

|------------------------|----------------------|--------------------------|--------------------------------------------|

| or                     | or \$\$1,\$\$2,\$\$3 | \$s1 =\$s2   \$s3        | Three register operands; bit-by-bit OR     |

| not                    | nor \$s1,\$s2,\$s3   | \$s1 = ~(\$s2  <br>\$s3) | Three register,operands; bit-by-bit<br>NOR |

| and immediate          | andi \$s1,\$s2,20    | \$s1 =\$s2 & \$20        | Bit-by-bit AND register with constant      |

| or immediate           | ori \$\$1,\$\$2,20   | \$s1 =\$s2   \$20        | Bit-by-bit OR register with constant       |

| shift left logical     | sll \$s1,\$s2,10     | \$s1 =\$s2 << 10         | Shift left by constant                     |

| shift right<br>logical | sr 1 \$s1,\$s2,10    | \$s1 =\$s2 >> 10         | Shift right lo by constant                 |

Example

## AND

- Useful to mask bits in a word •

- Select some bits, clear others to 0 and \$t0, \$t1, \$t2

## NOT

- Useful to invert bits in a word ۶

- Change 0 to 1, and 1 to 0

- 0000 0000 0000 0000 0011 1100 0000 0000 \$t1

- \$t0 1111 1111 1111 1111 1100 0011 1111 1111

SHIFT LEFT LOGICAL sll \$s1,\$s2,4 # reg \$t2 = reg \$s0 << 4 bits Before Execution For example, if register \$s0=9 0000 0000 0000 0000 0000 0000 0000 1001two= 9ten The instruction to shift left by 4 was executed, the new value would look like this: After Execution 0000 0000 0000 0000 0000 0000 1001 0000two= 144ten

#### 3. Data transfer Instructions

These instruction will transfer data between registers and main memory.

Examples: lw load word i.e. transfer of data from memory to register sw store word i.e. transfer of data from register to memory

Arithmetic operations occur only on registers in MIPS instructions; thus, MIPS must include instructions that transfer data between memory and registers. Such instructions are called data transfer instructions. To access a word in memory, the instruction must supply the memory address.Memory is just a large, single-dimensional array, with the address acting as the index to that array, starting at 0.

#### **EXAMPLE**

#### load word lw \$\$1,100(\$\$2) \$\$1 = Memory[\$\$2 + 100] Data from memory to register

The data transfer instruction that copies data from memory to a register is traditionally called *load*. The format of the load instruction is the name of the operation followed by the register to be loaded, then a constant and register used to access memory. The sum of the constant portion of the instruction and the contents of the second register forms the memory address.

#### store word sw \$s1,100(\$s2) Memory[\$s2 + 100] = \$s1 Data from register to memory

The data transfer instruction that copies data from Register to a Memory is traditionally called store.

| Instruction        | Example           | Meaning                     | Comments                                            |

|--------------------|-------------------|-----------------------------|-----------------------------------------------------|

| load word          | lw \$s1,20(\$s2)  | \$s1 = Memory (\$s2<br>+20) | Word from memory to register                        |

| store word         | sw \$s1,20(\$s2)  | Memory (\$s2 +20) =<br>\$s1 | Word from register to memory                        |

| load half          | lh \$s1,20(\$s2)  | \$s1 = Memory (\$s2<br>+20) | Half word memory to register                        |

| load half unsigned | lhu \$s1,20(\$s2) | \$s1 = Memory (\$s2<br>+20) | Half word memory to register                        |

| store half         | sh \$s1,20(\$s2)  | Memory (\$s2 +20) =<br>\$s1 | Half word register to memory                        |

| load byte          | lb \$s1,20(\$s2)  | \$s1 = Memory (\$s2<br>+20) | Byte from memory to register                        |

| load byte unsigned | lbu \$s1,20(\$s2) | \$s1 = Memory (\$s2<br>+20) | Byte from memory to register                        |

| store byte         | sb \$s1,20(\$s2)  | Memory (\$s2 +20) =<br>\$s1 | Byte from register to memory                        |

| load linked word   | ll \$s1,20(\$s2)  | \$s1 = Memory (\$s2<br>+20) | Load word as 1 <sup>st</sup> half of<br>atomic swap |

| store condition    | sc \$s1,20(\$s2)  | Memory (\$s2 +20) =         | store word as 2 <sup>nd</sup> half of               |

| word             |             | \$s1; \$s1=0 or 1         | atomic swap                        |

|------------------|-------------|---------------------------|------------------------------------|

| load upper immed | lui \$s1,20 | \$s1=20 * 2 <sup>16</sup> | Loads constant in upper 16<br>bits |

| Example: | add i \$\$1, \$\$2, 20 | # \$s1= \$s2+20         |

|----------|------------------------|-------------------------|

|          | lw \$s1, 20(\$s2)      | #\$s1=memory(\$s2+20)   |

|          | sw \$s1, 20(\$s2)      | #memory(\$s2+20) = \$s1 |

**Compiling an Assignment When an Operand Is in Memory**

Let's assume that A is an array of 100 words and that the compiler has associated the variables g and h with the registers \$\$1 and \$\$2 as before. Let's also assume that the starting address, or *base address*, of the array is in \$\$3. Compile this C assignment statement:

g = h + A[8];

Although there is a single operation in this assignment statement, one of the operands is in memory, so we must first transfer A[8] to a register. The address of this array element is the sum of the base of the array A, found in register \$ \$ , plus the number to select element 8. The data should be placed in a temporary register for use in the next instruction. the first compiled instruction is

1w \$t0.8(\$s3) # Temporary reg \$t0 gets A[8]

(We'll be making a slight adjustment to this instruction, but we'll use this simplified version for now.) The following instruction can operate on the value in t0 (which equals A[8]) since it is in a register. The instruction must add h (contained in s2) to A[8] (contained in t0) and put the sum in the register corresponding to g (associated with s1):

add \$s1,\$s2,\$t0 # g = h + A[8]

#### **Compiling Using Load and Store**

Assume variable h is associated with register \$52 and the base address of the array A is in \$53. What is the MIPS assembly code for the C assignment statement below?

A[12] = h + A[8]; 1w \$t0.32(\$s3) # Temporary reg \$t0 gets A[8] add \$t0.\$s2.\$t0 # Temporary reg \$t0 gets h + A[8] sw \$t0.48(\$s3) # Stores h + A[8] back into A[12]

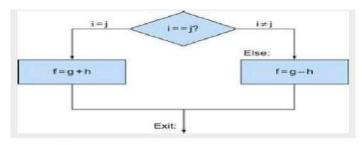

#### 4. Conditional Branch Instructions (DECISION MAKING)

These instruction will perform transfer the control from current location to target address

when the specified condition is satisfied otherwise control will go to next instructions.

Examples: beq branch on equal bne branch not equal

Branch instruction loads a new value into the program counter. As a result, the processor fetches and executes the instruction at this new address, called branch target, instead of executing in sequential order.

A Conditional branch instruction repeats the loop only if a specified condition is satisfied. If the condition is not satisfied it comes out of the loop.

Decision making is commonly represented in programming languages using the *if* statement, sometimes combined with *go to* statements and labels. MIPS assembly language includes two decision-making instructions, similar to an *if* statement with a *go to*.

## EXAMPLE

#### beq register1, register2, L1

This instruction means go to the statement labeled L1 if the value in register1 equals the value in register2. The mnemonic beq stands for *branch if equal*. The second instruction is

#### bne register1, register2, L1

It means go to the statement labeled L1 if the value in register1 does *not* equal the value in register2. The mnemonic bne stands for *branch if not equal*. These two instructions are traditionally called conditional branches.

#### **Conditional Branch Instructions**

| Instruction                  | Example                | Meaning                                     | Comments                         |

|------------------------------|------------------------|---------------------------------------------|----------------------------------|

| branch on equal              | beq \$s1,\$s2,25       | if(\$s1 == \$s2) go t<br>o PC + 4 +100      | Equal test ; PC- relative branch |

| branch on not<br>equal       | bne \$s1,\$s2,25       | if(\$s1!= \$s2) go t o<br>PC + 4 +100       | Not equal test ; PC- relative    |

| set on less than             | slt \$s1,\$s2,\$s3     | if(\$s2 < \$s3)<br>\$s1=1;<br>else \$s1 = 0 | Compare less than for beq, bne   |

| set on less than<br>unsigned | sltu<br>\$s1,\$s2,\$s3 | if(\$s2 < \$s3)<br>\$s1=1;<br>else \$s1 = 0 | Compare less than unsigned       |

| set on less than             | slti \$s1,\$s2,20      | if(\$s2 < 20) \$s1=1;                       | Compare less than constant       |

| immediate                                 |                    | else \$s1 = 0                          |                                     |

|-------------------------------------------|--------------------|----------------------------------------|-------------------------------------|

| set on less than<br>immediate<br>unsigned | sltiu \$s1,\$s2,20 | if(\$s2 < 20) \$s1=1;<br>else \$s1 = 0 | Compare less than constant unsigned |

#### Example:

**Compiling IF statements:**

C code:

```

if (i==j) f = g+h;

else f = g-h;

• f, g, ... in $s0, $s1, ...

Compiled MIPS code:

bne $s3, $s4, Else

add $s0, $s1, $s2

j Exit

Else: sub $s0, $s1, $s2

Exit:

Assembler calculates accreases

```

## 5. Unconditional Jump Instructions

These instructions will transfer control from current location to target address.

Examples: J: jump to transfer address

jr: jump to target address available in register \$ra used for procedure return.

jal: load the return address (PC+4 )into register \$ra and jump to target address, used for procedure call.

Note: MIPS processor has no I/O Instructions.

| Instruction   | Example  | Meaning                       | Comments                     |

|---------------|----------|-------------------------------|------------------------------|

| jump          | j 2500   | go to 10000                   | Jump to target address       |

| jump register | jr \$ra  | go to \$ra                    | For switch, procedure return |

| jump and link | jal 2500 | \$ra = PC + 4; go to<br>10000 | For procedure call           |

## C code:

while (save[i] == k) i += 1; i in \$s3, k in \$s5, address of save in \$s6 Compiled MIPS code:

```

Loop: sll $t1, $s3, 2

add $t1, $t1, $s6

lw $t0, 0($t1)

bne $t0, $s5, Exit

addi $s3, $s3, 1

j Loop

Exit: ...

```

## **OPERANDS AVAILABLE IN MIPS**

MIPS instruction uses three type of operands

1. Register 2. Memory 3. Immediate

1.

Register: MIPS processor has 32 registers.

The size of the register is 32 bits. These registers are represented by 5 bit binary number in the MIPS instruction and they are referred by 2 or 3 character name in MIPS assembly code.

#\$t1=\$s1+\$s2

Example: add \$t1, \$s1, \$s2

Name **Register number** Usage 0 The constant value 0 \$zero 2 - 3Values for results and expression evaluation \$v0-\$v1 \$a0-\$a3 4-7 Arguments 8-15 Temporaries \$t0-\$t7 16-23 Saved \$\$0-\$\$7 24-25 \$t8-\$t9 More temporaries 28 \$gp Global pointer \$sp 29 Stack pointer 30 \$fp Frame pointer 31 Return address \$ra

## 2. Memory

Since arithmetic and logic instructions use only register operands, MIPS need instruction to transfer data between memory & register. Such instruction are called Data Transfer instructions.

The instruction which transfer the data from memory to register is called Load.

Example: lw \$t0, 8(\$s1)

| Ist operand   | Register operand |

|---------------|------------------|

| II nd operand | Memory operand   |

| 8             | is called offset |

is called base register

- To get the proper memory address, the offset to be added to base registers \$s1.

- Normally base register \$s1 will have address of data array

- The offset 8 permits to get second element of data array.

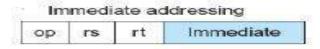

## 3. Immediate

Many times, a program will use a constant in an operation for example incrementing an index to point to the next element of an array. This constant field size is 16 bit that permits  $\pm 2^{15}(32768)$ .

| Example: | add i \$s3,\$s3,4 | # \$s3 =\$s3+4 |

|----------|-------------------|----------------|

|          | add i \$s3,\$s3,1 | #\$s3 =\$s3+1  |

## ADDRESSING MODES OF MIPS

**\$**s1

The different ways in which the address of the operand is specified in an instruction is called addressing mode. The addressing modes vary from one computer to another MIPS processor supports the following five addressing modes.

1. Immediate addressing, where the operand is a constant within the instruction itself.

2. Register addressing, where the operand is a register.

3. Base or displacement addressing, where the operand is at the memory location whose address is the sum of a register and a constant in the instruction.

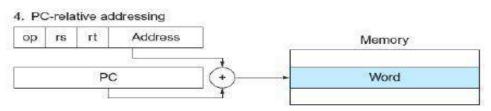

4. PC-relative addressing, where the branch address is the sum of the PC and a constant in the instruction.

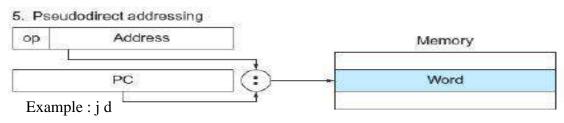

5. Pseudodirect addressing, where the jump address is the 26 bits of the instruction concatenated with the upper Four bits of the PC.

1. Immediate addressing: The operand is a constant within the instructionitself. i.e. The operand is specified in the instruction itself.

Example: Add i \$t1, \$s1,d

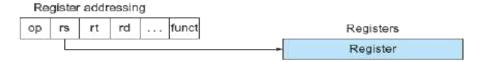

2. Register addressing: The operand is in a CPU register. The register is specified in the instruction.

Example: add \$t1, \$S1, \$S2

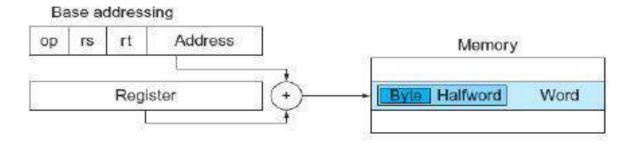

3. **Base or displacement addressing:** The operand is at the memory location whose address is the sum of a register and a constant in the instruction.

Here the operand is a memory location whose address is the sum of register (base register) and a constant (offset/displacement)

Example: lw \$s1, 20(\$s2)

4. PC-relative addressing: The branch address is the sum of the PC and a constant in the instruction.

Example :beq \$rs, \$rt, d

5. *Pseudo-direct addressing: The jump address is the 26 bits of the* instruction concatenated with the upper Four bits of the PC.

## REPRESENTATION OF INSTRUCTION (INSTRUCTION FORMAT)

- 1. <u>**R-TYPE : Used in arithmetic Instruction</u>**</u>

- 2. I-type : used in data transfer instruction and conditional branch instruction

- 3. J-type: used in unconditional branch instructions.

## **R-TYPE:**

This instruction format is called R type and used for arithmetic and logic instruction.

| ор     | rs     | rt     | rd     | shamt  | funct  |

|--------|--------|--------|--------|--------|--------|

| 6 bits | 5 bits | 5 bits | 5 bits | 5 bits | 6 bits |

The meaning of each field is given below

- op : Basic operation of the instruction (op code)

- rs : The first register source field

- rt : The second register source field

- rd : The register destination field get the result

- shamt: shift amount for shift instruction and zero for other

instruction

• funct : called function code specific variant of the operation in the op field

All register field are 5 bit to refer any one of the 32 MIPS registers. Example : add \$t0, \$s1, \$s2 # \$t0=\$s1+\$s2

#### **<u>I-TYPE:</u>** This is used for immediate as well as data transfer

|     | ор     | rs     | rt     | constant or address |  |

|-----|--------|--------|--------|---------------------|--|

| - 0 | 6 bits | 5 bits | 5 bits | 16 bits             |  |

instruction.

The meaning of each field is given below

- op : op code

- rs : The first register source field

- rt : register destination for load & source for store

- constant or address : constant is used in immediate instruction and address is used in data transfer instruction

This format is used for branch instruction and it is similar to I type.

| ор     | rs     | rt     | address |

|--------|--------|--------|---------|

| 6 bits | 5 bits | 5 bits | 16 bits |

The meaning of each field is given below

- op : op code

- rs : The first register source field

- rt : Second register source field

- address : address is used in branch instruction

Example :beq \$1, \$2, d #if(\$1=\$2) goto (PC+4+(4\*d))

iii) J-TYPE: This instruction format is used for jump instruction called J type.

| op     | address |

|--------|---------|

| 6 bits | 26 bits |

The meaning of each field is given below

WHERE op : op code and Address : used in jump

Example : j d # go to 4\*d

## UNIT II ARITHMETIC OPERATIONS

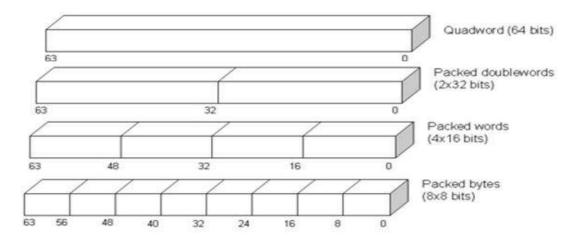

## ALU - Addition and subtraction – Multiplication – Division – Floating Point operations Subword parallelism.

## ARITHEMETIC AND LOGICAL UNIT

The arithmetic logic unit (ALU) performs

- The arithmetic operations like addition and subtraction.

- Logical operations like AND and OR.

Because the MIPS word is 32 bits wide, we need a 32-bit-wide ALU. Let's assume that we will connect 32 1-bit ALUs to create the desired ALU.

## **ALU-ADDITION**

## 1-Bit MIPS ALU 1.1 HALF ADDER

**Truth table :**CarryOut =  $(b \cdot CarryIn) + (a \cdot CarryIn) + (a \cdot b) + (a \cdot b \cdot CarryIn)$

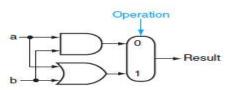

FIGURE C.5.1 The 1-bit logical unit for AND and OR.

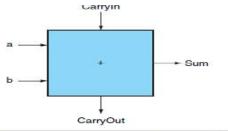

FIGURE C.5.2 A 1-bit adder. This adder is called a full adder; it is also called a (3,2) adder because it has 3 inputs and 2 outputs. An adder with only the a and b inputs is called a (2,2) adder or half-adder.

## FULL ADDER

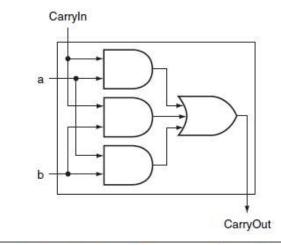

FIGURE C.5.5 Adder hardware for the CarryOut signal. The rest of the adder hardware is the logic for the Sum output given in the equation on this page.

The Sum bit is set when exactly one input is 1 or when all three inputs are 1. The Sum results in a complex Boolean equation (recall that  $\overline{a}$  means NOT a):

$Sum = (a \cdot \overline{b} \cdot \overline{CarryIn}) + (\overline{a} \cdot b \cdot \overline{CarryIn}) + (\overline{a} \cdot \overline{b} \cdot CarryIn) + (a \cdot b \cdot CarryIn)$

The multiplexer selects AND or OR or adder output based on the value of operation 0(00) or 1 (01) or

2(10). The adder takes three input (two digits & one carry from previous stage) and produce sum and carry outputs, and it is called full adder. The truth table is shown below.

|   | Inputs |         | Outputs  |     |                        |  |

|---|--------|---------|----------|-----|------------------------|--|

| a | b      | Carryin | CarryOut | Sum | Comments               |  |

| 0 | 0      | 0       | 0        | 0   | $0 + 0 + 0 = 00_{two}$ |  |

| 0 | 0      | 1       | 0        | 1   | $0 + 0 + 1 = 01_{two}$ |  |

| 0 | 1      | 0       | 0        | 1   | $0 + 1 + 0 = 01_{two}$ |  |

| 0 | 1      | 1       | 1        | 0   | $0 + 1 + 1 = 10_{two}$ |  |

| 1 | 0      | 0       | 0        | 1   | $1 + 0 + 0 = 01_{two}$ |  |

| 1 | 0      | 1       | 1        | 0   | $1 + 0 + 1 = 10_{two}$ |  |

| 1 | 1      | 0       | 1        | 0   | $1 + 1 + 0 = 10_{two}$ |  |

| 1 | 1      | 1       | 1        | 1   | $1 + 1 + 1 = 11_{two}$ |  |

#### The logic expression for sum is

$Sum = (a \cdot \overline{b} \cdot \overline{CarryIn}) + (\overline{a} \cdot b \cdot \overline{CarryIn}) + (\overline{a} \cdot \overline{b} \cdot CarryIn) + (a \cdot b \cdot CarryIn)$

The logical expression for carryout

$CarryOut = (b \cdot CarryIn) + (a \cdot CarryIn) + (a \cdot b)$

## is

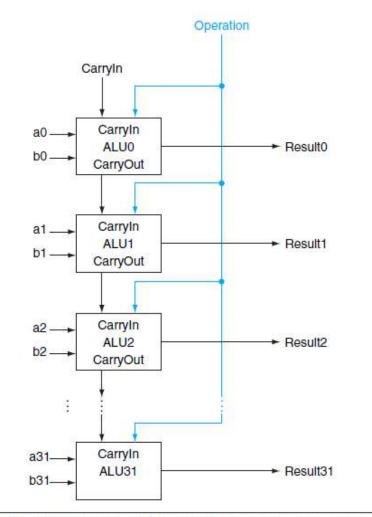

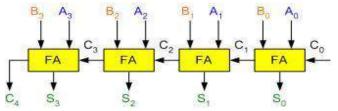

**32 BITS ADDER**

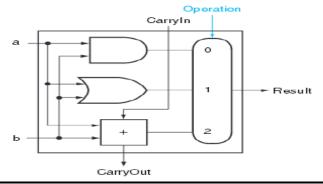

32 bit ALU can be constructed by connecting 32 1-bit ALU in cascade. 1-bit ALU with logical unit for AND

and OR and adder is shown below.

FIGURE C.5.7 A 32-bit ALU constructed from 32 1-bit ALUs. CarryOut of the less significant bit is connected to the CarryIn of the more significant bit. This organization is called ripple carry.

## **ALU MIPS SUBTRACTION**

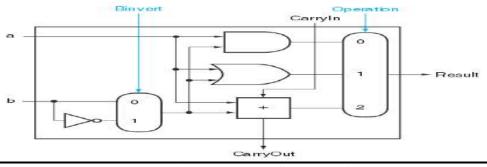

Subtraction is the same as adding the negative version of an operand and this is how adder performs subtraction. For negating a 2's complement number is to invert each bit and add 1. To invert each bit, 2:1 multiplexer chooses between b and b as in **Fig .3**

Fig 3: 1-Bit ALU with AND, OR, ADD and SUBTRACT

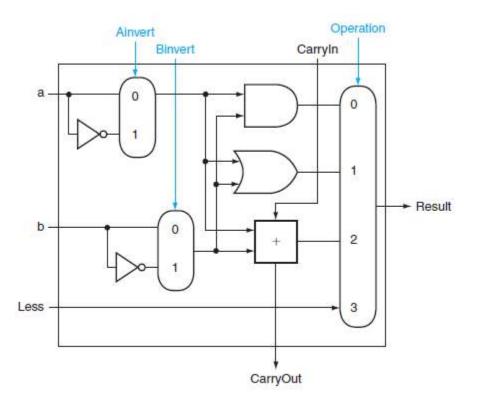

These four operations—add, subtract, AND, OR—are found in the ALU of almost every computer, and the operations of most MIPS instructions can be performed by this ALU. But the design of the ALU is incomplete. One instruction that still needs support is the set on less than instruction (slt). Recall that the operation produces 1 if rs < rt, and 0 otherwise. Consequently, slt will set all but the least significant bit to 0, with the least significant bit set according to the comparison. For the ALU to perform slt, we first need to expand the three-input multiplexor in above figure to add an input for the slt result. We call that new input Less and use it only for slt.

From the description of slt above, we must connect 0 to the Less input for the upper 31 bits of the ALU, since those bits are always set to 0. What remains to consider is how to compare and set the least significant bit for set on less than instructions.

What happens if we subtract b from a?

If the difference is negative, then a < b since  $(a - b) < 0 \Rightarrow ((a - b) + b) < (0 + b) \Rightarrow a < b$

We want the least significant bit of a set on less than operation to be a 1 if a < b;

that is, a 1 if a - b is negative and a 0 if it's positive.

This desired result corresponds exactly to the sign bit values:

1 means negative and 0 means positive.

Following this line of argument, we need only connect the sign bit from the adder output to the least significant

bit to get set on less than.

Unfortunately, the Result output from the most significant ALU bit in the top of Figure C.5.10 for the slt operation is not the output of the adder; the ALU output for the slt operation is obviously the input value Less.

Thus, we need a new 1-bit ALU for the most significant bit that has an extra output bit: the adder output. The bottom drawing of Figure C.5.10 shows the design, with this new adder output line called Set, and used only for slt.

As long as we need a special ALU for the most significant bit, we added the overflow detection logic since it is also associated with that bit.

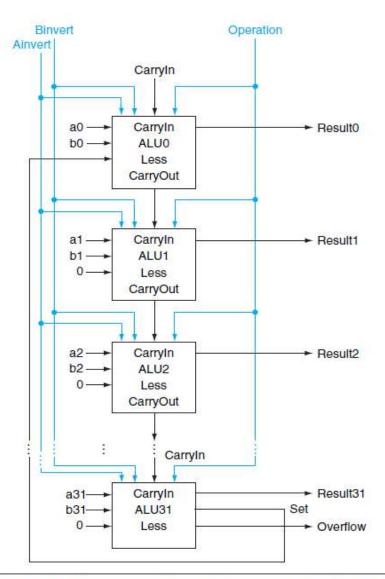

## <u>32 bits</u>

**FIGURE C.5.11** A 32-bit ALU constructed from the 31 copies of the 1-bit ALU in the top of Figure C.5.10 and one 1-bit ALU in the bottom of that figure. The Less inputs are connected to 0 except for the least significant bit, which is connected to the Set output of the most significant bit. If the ALU performs a - b and we select the input 3 in the multiplexor in Figure C.5.10, then Result = 0...001 if a < b, and Result = 0...000 otherwise.

Subtraction

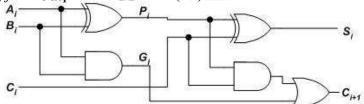

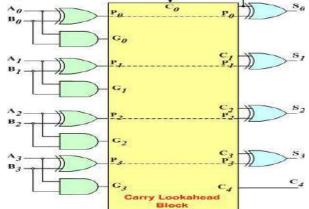

#### **Carry Look Ahead Adder:**

In *ripple carry adders*, the carry propagation time is the major speed limiting factor as seen in the previous lesson.

Most other arithmetic operations, e.g. multiplication and division are implemented using several add/subtract steps. Thus, improving the speed of addition will improve the speed of all other arithmetic operations.

Accordingly, reducing the carry propagation delay of adders is of great importance. Different logic design approaches have been employed to overcome the carry propagation problem. One widely used approach employs the principle of *carry look-ahead* solves this problem by calculating the carry signals in advance, based on the input signals.

This type of adder circuit is called as *carry look-ahead adder (CLA adder)*. It is based on the fact that a carry signal will be generated in two cases:

(1) when both bits  $A_i$  and  $B_i$  are 1, or

(2) when one of the two bits is 1 and the carry-in (carry of the previous stage) is 1.

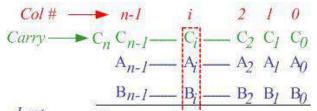

To understand the carry propagation problem, let's consider the case of adding two *n-bit* numbers A and B.

The Figure shows the full adder circuit used to add the operand bits in the *i*<sup>th</sup> column; namely  $A_i \& B_i$  and the carry bit coming from the previous column ( $\overline{C_i}$ ).

In this circuit, the 2 internal signals *P<sub>i</sub>* and *G<sub>i</sub>* are given by:

$Pi = Ai \bigoplus Bi$  .....(1)

Gi = Ai Bi .....(2)

#### The output sum and carry can be defined as :

$Si = Pi \bigoplus Ci$  .....(3) Ci + 1 = Gi + Pi Ci .....(4)

**G**<sub>i</sub> is known as the **carry Generate** signal since a carry ( $C_{i+1}$ ) is generated whenever  $G_i = 1$ , regardless of the input carry ( $C_i$ ).**P**<sub>i</sub> is known as the **carry propagate** signal since whenever  $P_i = 1$ , the input carry is propagated to the output carry, i.e.,  $C_{i+1} = C_i$  (note that whenever  $P_i = 1$ ,  $G_i = 0$ ).Computing the values of  $P_i$  and  $G_i$  only depend on the input operand bits ( $A_i \& B_i$ ) as clear from the Figure and equations. Thus, these signals settle to their **steady-state value** after the propagation through their respective gates. Computed values of **all** the  $P_i$ 's are valid one XOR-gate delay after the operands A and B are made valid. Computed values of **all** the  $G_i$ 's are valid one AND-gate delay after the operands A and B are made valid.

#### The Boolean expression of the carry outputs of various stages can be written as follows:

$\mathbf{C}_1 = \mathbf{G}_0 + \mathbf{P}_0 \mathbf{C}_0$

$C_2 = G_1 + P_1C_1 = G_1 + P_1 (G_0 + {}_0C_0) = G_1 + P_1G_0 + P_1P_0C_0$

$C_3 = G_2 + P_2C_2 = G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0C_0$

$C_4 = G_3 + P_3C_3 = G_3 + P_3G_2 + P_3P_2G_1 + P_3P_2P_1G_0 + P_3P_2P_1P_0C_0$

In general, the *i*<sup>th</sup> carry output is expressed in the form  $C_i = F_i$  (P's, G's, C<sub>0</sub>).

In other words, each carry signal is expressed as a direct SOP function of  $C_0$  rather than its preceding carry signal. Since the Boolean expression for each output carry is expressed in SOP form, it can be implemented in two-level circuits. The 2-level implementation of the carry signals has a propagation delay of 2 gates, i.e.,  $2\tau$ .

#### The 4-bit carry look-ahead (CLA) adder consists of 3 levels of logic:

**First level:** Generates all the P & G signals. Four sets of P & G logic (each consists of an XOR gate and an AND gate). Output signals of this level (P's & G's) will be valid after  $1\tau$ .

**Second level:** The Carry Look-Ahead (CLA) logic block which consists of four 2-level implementation logic circuits. It generates the carry signals ( $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ ) as defined by the above expressions. Output signals of this level ( $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ ) will be valid after  $3\tau$ .

**Third level:** Four XOR gates which generate the sum signals  $(S_i)$   $(S_i = P_i \bigoplus C_i)$ . Output signals of this level  $(S_0, S_1, S_2, \text{ and } S_3)$  will be valid after  $4\tau$ .

## **MULTIPLICATION**

| The basics multiplication (The traditional Approach) |         |                                    |  |  |  |  |

|------------------------------------------------------|---------|------------------------------------|--|--|--|--|

| Multiplying 1000ten by 1001ten                       |         |                                    |  |  |  |  |

| Multiplicand                                         |         | 1000ten                            |  |  |  |  |

| Multiplier                                           | x       | <u>1001ten</u>                     |  |  |  |  |

|                                                      |         | 1000                               |  |  |  |  |

| 0000                                                 |         |                                    |  |  |  |  |

| 0000                                                 |         |                                    |  |  |  |  |

| 1000                                                 |         |                                    |  |  |  |  |

| Product                                              |         | 1001000ten                         |  |  |  |  |

| • The first                                          | st oper | and is called the <b>multiplic</b> |  |  |  |  |

- The first operand is called the **multiplicand** and the second the **multiplier**. The final result is called the **product**.

- The length of the multiplication of an *n*-bit multiplicand and an *m*-bit multiplier is a product that is *n* + *m* bits long. That is, *n* + *m* bits are required to represent all possible products. Hence, like add, multiply must cope with overflow because we frequently want a 32-bit product as the result of multiplying two 32-bit numbers.

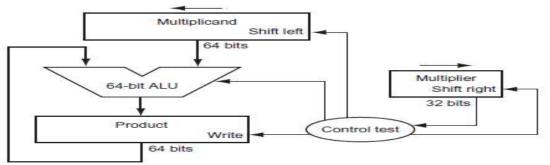

## **<u>MULTIPLICATION HARDWARE</u>** The following fig shows hardware for 32 bit multiplication

In the Hardware Diagram, Let's assume that the multiplier is in the 32-bit Multiplier register and that the 64-bit Product register is initialized to 0. It's clear that we will need to move the multiplicand left one digit each step, as it may be added to the intermediate products. Over 32 steps, a 32-bit multiplicand would move 32 bits to the left. Hence, we need a 64-bit Multiplicand register, initialized with the 32-bit multiplicand in the right half and zero in the left half. This register is then shifted left 1 bit each step to align the multiplicand with the sum being accumulated in the 64-bit Product register.

## **Multiplication Hardware Diagram**

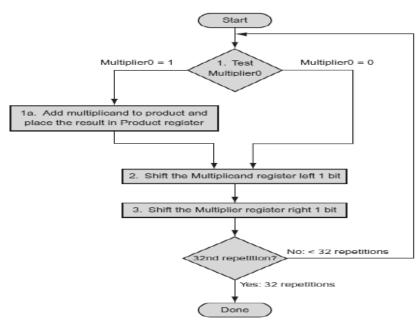

## MULTIPLICATION ALGORITHM

## Three basic steps are required for each bit of multiplier.

- Step1. The least significant bit of multiplier is examined ,if 1 add multiplicand with product otherwise no add

- Step2. Multiplicand register is shifted left by one bit

- Step3. Multiplier register is shifted right by one bit

These 3 steps are repeated 32 times and at the end product is available in product register.

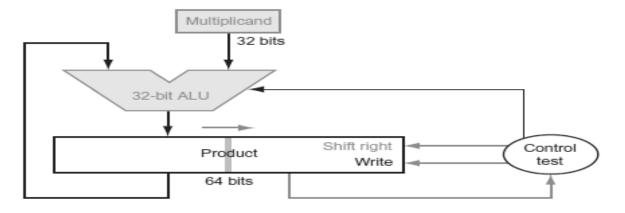

The hardware is further optimized to adder with 32 bit and multiplicand register with 32 bit, no multiplier register and product register of 64 bit.

## **Example**

Using 4-bit numbers to save space, multiply **2ten X 3ten, or 0010two X 0011two**. Figure 3.6 shows the value of each register for each of the steps labeled according to Figure 3.4, with the final value of 0000 0110two or

6ten.

| Iteration | Step                                        | Multiplier | Multiplicand | Product   |

|-----------|---------------------------------------------|------------|--------------|-----------|

| 0         | Initial values                              | 0011       | 0000 0010    | 0000 0000 |

| 1         | 1a: 1 $\Rightarrow$ Prod = Prod + Mcand     | 0011       | 0000 0010    | 0000 0010 |

|           | 2: Shift left Multiplicand                  | 0011       | 0000 0100    | 0000 0010 |

|           | 3: Shift right Multiplier                   | 0000       | 0000 0100    | 0000 0010 |

| 2         | 1a: $1 \Longrightarrow Prod = Prod + Mcand$ | 0001       | 0000 0100    | 0000 0110 |

|           | 2: Shift left Multiplicand                  | 0001       | 0000 1000    | 0000 0110 |

|           | 3: Shift right Multiplier                   | 0000       | 0000 1000    | 0000 0110 |

| 3         | 1: $0 \Rightarrow No operation$             | 0000       | 0000 1000    | 0000 0110 |

|           | 2: Shift left Multiplicand                  | 0000       | 0001 0000    | 0000 0110 |

|           | 3: Shift right Multiplier                   | 0000       | 0001 0000    | 0000 0110 |

| 4         | 1: $0 \Rightarrow No operation$             | 0000       | 0001 0000    | 0000 0110 |

|           | 2: Shift left Multiplicand                  | 0000       | 0010 0000    | 0000 0110 |

|           | 3: Shift right Multiplier                   | 0000       | 0010 0000    | 0000 0110 |

FIGURE 3.6 Multiply example using algorithm in Figure 3.4. The bit examined to determine the next step is circled in color.

## MULTIPLICATION FLOWCHART

## **REFI NED VERSION OF THE MULTIPLICATION HARDWARE**

Compare with the first version. The Multiplicand register, ALU, and Multiplier register are all 32 bits wide, with only the Product register left at 64 bits. Now the product is shifted right. The separate Multiplier register also disappeared. The multiplier is placed instead in the right half of the Product register.

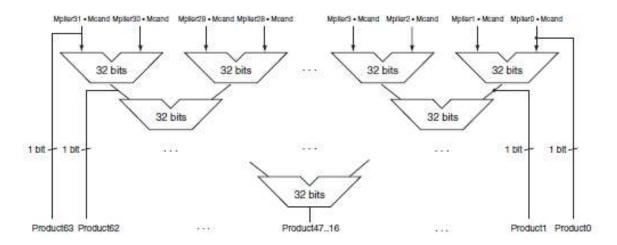

## FASTER MULTIPLICATION:

- Moore's Law has provided so much more in resources that hardware designers can now build much faster multiplication hardware. Whether the multiplicand is to be added or not is known at the beginning of the multiplication by looking at each of the 32 multiplier bits.

- Faster multiplications are possible by essentially providing one 32-bit adder for each bit of the multiplier: one input is the multiplicand ANDed with a multiplier bit, and the other is the output of a prior adder.

- A straightforward approach would be to connect the outputs of adders on the right to the inputs of adders on the left, making a stack of adders 32 high.

- An alternative way to organize these 32 additions is in a parallel tree shows. Instead of waiting for 32 add times, we wait just the log2 (32) or five 32-bitadd times.

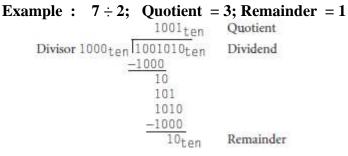

#### **<u>DIVISION</u>** Basic Division Operation

The hardware division is identical to school division algorithm.

Divide's two operands, called the **dividend** and **divisor**, and the result, called the **quotient**, are accompanied by a second result, called the **remainder**. Here is another way to express the relationship between the components: Dividend \_ Quotient \_ Divisor \_ Remainder

where the remainder is smaller than the divisor.

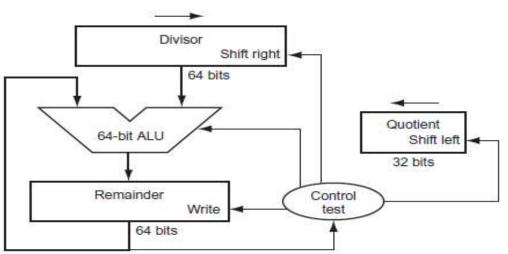

## **DIVISION HARDWARE**

To start with 32 bit quotient register set to 0. Since each iteration divisor need to be shifted right by one digit, start with the divisor is placed in the left half of 64 bit DIVISIOR register and shift right by 1 bit each step to align with the dividend. The remainder register is initialized with dividend

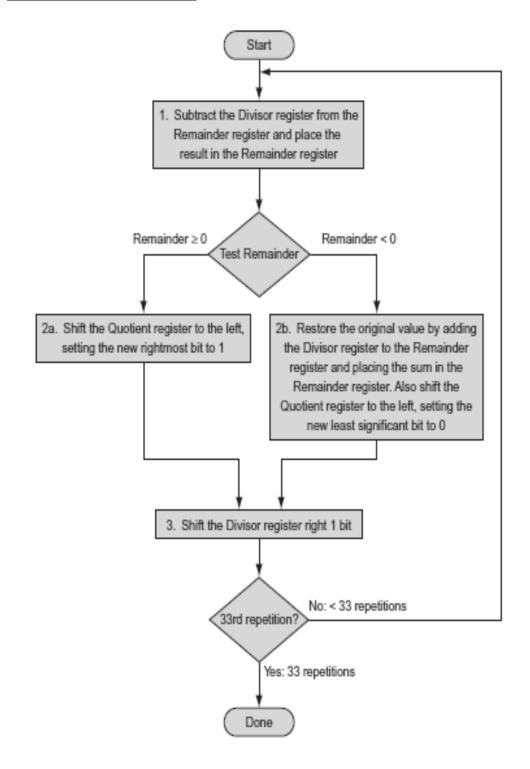

## **DIVISION ALGORITHM**

Three basic steps are.

**Step1:** Subtract divisor register from remainder register place the result in remainder register.

Step1 A: If the reminder is +ve. Shift the quotient register to the left and set Qo=1

**Step2B**: If the remainder is –ve. Restore the original value by adding the

DIVISOR register to the remainder register and place the result in remainder register and also shift the quotient register to the left and set Qo = 0.

**Step 3:** Shift the divisor right by 1 bit. Repeat these three steps 33 times and at the end remainder and quotient are available in the corresponding registers. This is called **Restoring Division**.

## **DIVISION FLOW CHART**

| teration | Step                                          | Quotient | Divisor   | Remainder  |

|----------|-----------------------------------------------|----------|-----------|------------|

| 0        | Initial values                                | 0000     | 0010 0000 | 0000 0111  |

| 1        | 1: Rem = Rem - Div                            | 0000     | 0010 0000 | (J110 0111 |

|          | 2b: Rem < 0 ⇒ +Div, sll Q, Q0 = 0             | 0000     | 0010 0000 | 0000 0111  |

|          | 3: Shift Div right                            | 0000     | 0001 0000 | 0000 0111  |

| 2        | 1: Rem = Rem - Div                            | 0000     | 0001 0000 | ()111 0111 |

|          | 2b: Rem < 0 ⇒ +Div, sll Q, Q0 = 0             | 0000     | 0001 0000 | 0000 0111  |

|          | 3: Shift Div right                            | 0000     | 0000 1000 | 0000 0111  |

| 3        | 1: Rem = Rem - Div                            | 0000     | 0000 1000 | @111 1111  |

|          | 2b: Rem < 0 $\Rightarrow$ +Div, sll Q, Q0 = 0 | 0000     | 0000 1000 | 0000 0111  |

|          | 3: Shift Div right                            | 0000     | 0000 0100 | 0000 0111  |

| 4        | 1: Rem = Rem - Div                            | 0000     | 0000 0100 | 0000 0011  |

|          | 2a: Rem≥0 ⇒ sll Q, Q0 = 1                     | 0001     | 0000 0100 | 0000 0011  |

|          | 3: Shift Div right                            | 0001     | 0000 0010 | 0000 0011  |

| 5        | 1: Rem = Rem - Div                            | 0001     | 0000 0010 | 0000 0001  |

|          | 2a: Rem≥0 ⇒ sil Q, Q0 = 1                     | 0011     | 0000 0010 | 0000 0001  |

|          | 3: Shift Div right                            | 0011     | 0000 0001 | 0000 0001  |

FIGURE 3.10 Division example using the algorithm in Figure 3.9. The bit examined to determine the next step is circled in color.

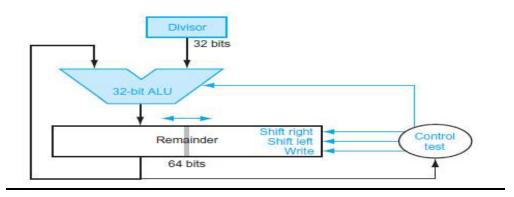

## AN IMPROVED VERSION OF THE DIVISION HARDWARE.

The Divisor register, ALU, and Quotient register are all 32 bits wide, with only the Remainder register left at 64 bits the ALU and Divisor registers are halved and the remainder is shifted left.

The hardware is further optimized with divisor register and Adder 32-bit wide with only reminder register left at 64 bits. This version also combines the Quotient register with the right half of the Remainder register.

# **FLOATING POINT OPERATIONS**

# **IEEE standards for Binary Arithmetic operations for floating point numbers**

Includes Fraction and Exponent

## Representation of ARM(Advanced RISC machine) Floating-point Number

- $S \rightarrow Sign$  of the floating point number

- $E \rightarrow$  Value of the 8-bit exponent field

- $F \rightarrow 23$ -bit number

- Single Precision Format

### Format of Floating point number

$(-1)^{s} \times F \times 2^{E}$

- Overflow Interrupt occurs in Floating-point Arithmetic

- Overflow  $\rightarrow$  Positive Exponent is too large to be represented in the Exponent field

- Underflow  $\rightarrow$  Negative Exponent is too large to be represented in the Exponent field

- To reduce the chances of Underflow and overflow

- Another format is used has a larger exponent

- Double Precision floating-point arithmetic

- Both called IEEE 754 Floating-point Standard invented in 1980

- Double Precision floating-point

- S  $\rightarrow$  Sign of the floating point number

- $E \rightarrow$  Value of the 11-bit exponent field

- $F \rightarrow 32$ -bit number

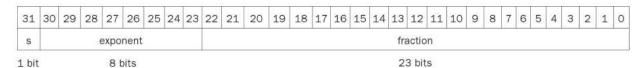

| 31   | 30                   | 29       | 28 | 27 | 26 | 25 | 24 | 23       | 22      | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|----------------------|----------|----|----|----|----|----|----------|---------|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| s    |                      | exponent |    |    |    |    |    | fraction |         |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| 1 bi | t                    | 11 bits  |    |    |    |    |    |          | 20 bits |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|      | fraction (continued) |          |    |    |    |    |    |          |         |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

32 bits

| Constant and the second second | 64 bits                                                             |                  |

|--------------------------------|---------------------------------------------------------------------|------------------|

| S                              | Hund Knew grounder M-roogen bigget owne                             | ion and          |

|                                |                                                                     | 100 Jacob (1997) |

| 11-bit excess-1023<br>exponent | 52-bit<br>mantissa fraction                                         |                  |

| exponent                       | mantissa fraction<br>e represented = $\pm 1.M \times 2^{E' - 1023}$ |                  |

Exponent bias is 127 for single-precision

1023 for double-precision

Representation

• sign, exponent, significand

$(-1)^{\text{sign}} \times \text{significand} \times 2^{\text{exponent}}$

- more bits for significand gives more accuracy

- more bits for exponent increases range

*Exponent => range, significand => precision*

#### Example

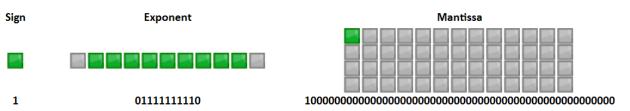

IEEE 754 binary Representation of the number -0.7510 in Single and Double Precision

Number  $-0.75_{10}$  is also  $-3/4_{ten}$  or  $-3/2^2_{ten}$

Represented in binary fraction  $-11/2^{2}_{ten}$

Scientific Notation -0.11 $_{two}$  x  $2^0$

Normalized into  $-1.1_{two} \ge 2^{-1}$

-1.1two x 2<sup>-1</sup>

Single precision representation

$$x = (-1)^{S} \times (1 + Fraction) \times 2^{(Exponent-Bias)}$$

Subtracting the bias 127 from the exponent

**Single:**  $-1 + 127 = 126 = 01111110_2$

#### Underflow and Overflow in single precision

- In single precision floating point representation exponent is represented in excess 127

- Total exponent field range is -127 to +128

- Since +128 and -127 are used for special case, real exponent range is -126 to +127

- If the exponent exceeds +127 it is called overflow

- If the exponent is < -126 it is called underflow

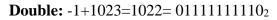

### Underflow and Overflow in double precision

- In double precision floating point representation exponent is represented in excess 1023

- Total exponent field range is -1023 to +1024

- Since -1023 and +1024 are used for special case, real exponent range is -1022 to +1023

- If the exponent exceeds +1023 it is called overflow

- If the exponent is < -1022 it is called underflow

### NORMALIZATION

### Normalization of Floating Point Number

In floating point the number is always put in normalized form. By convention when the decimal point is placed to the right of first significant digit, the number is said to be normalized.

#### Example of unnormalized number

|                 | .001 | $0110 \ge 2^9$                               |

|-----------------|------|----------------------------------------------|

| Normalized Form | =    | 1.0110 X (2 <sup>9</sup> X 2 <sup>-3</sup> ) |

|                 | =    | 1.0110 X 2 <sup>6</sup>                      |

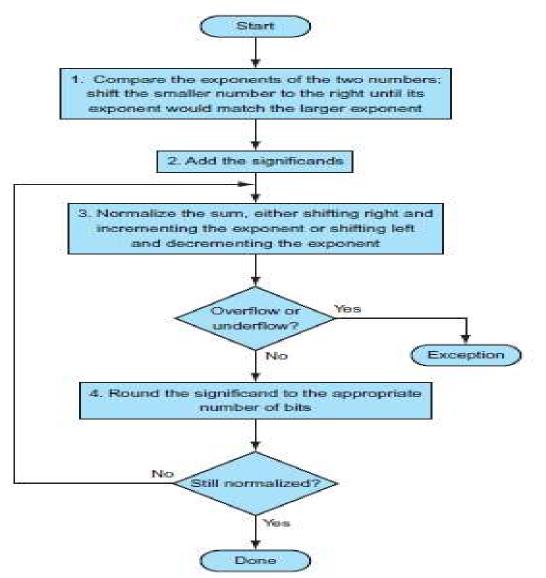

# FLOATING POINT ADDITION FLOATING POINT ADDITION ALGORITHM

# The following steps gives the algorithm for IEEE floating point addition(also indicated in the flow chart..

**Step 1**:Compare the exponents of two numbers and shift the number with smaller exponent, until the exponent matches the larger exponent.

Step 2: Add the significands.

Step 3:Normalize the result if required either shift right and increment exponent or shift left and decrement the exponent and check for overflow / under flow.

Step 4:Round the significant to appropriate number of bits normalize if required and check for overflow / underflow.

### FLOWCHART:

Explain how floating point addition is carried out in a computer system. Give an example for a binary floating point addition.

#### Floating-Point Addition

Let's add numbers in scientific notation by hand to illustrate the problems in floating-point addition:  $9.999_{ten} \times 10^{1} + 1.610_{ten} \times 10^{-1}$ . Assume that we can store only four decimal digits of the significand and two decimal digits of the exponent.

Step 1. To be able to add these numbers properly, we must align the decimal point of the number that has the smaller exponent. Hence, we need a form of the smaller number,  $1.610_{ten} \times 10^{-1}$ , that matches the larger exponent. We obtain this by observing that there are multiple representations of an unnormalized floating-point number in scientific notation:

$$1.610_{-1} \times 10^{-1} = 0.1610_{-1} \times 10^{0} = 0.01610_{-1} \times 10^{10}$$

The number on the right is the version we desire, since its exponent matches the exponent of the larger number,  $9.999_{ten} \times 10^1$ . Thus, the first step shifts the significand of the smaller number to the right until its corrected exponent matches that of the larger number. But we can represent only four decimal digits so, after shifting, the number is really

$$0.016 \times 10^{1}$$

Step 2. Next comes the addition of the significands:

$$+ \frac{9.999_{ten}}{10.016_{ten}}$$

The sum is  $10.015_{ten} \times 10^1$ .

Step 3. This sum is not in normalized scientific notation, so we need to adjust it:

$$10.015_{\text{tm}} \times 10^3 = 1.0015_{\text{tm}} \times 10^2$$

Thus, after the addition we may have to shift the sum to put it into normalized form, adjusting the exponent appropriately. This example shows shifting to the right, but if one number were positive and the other were negative, it would be possible for the sum to have many leading 0s, requiring left shifts. Whenever the exponent is increased or decreased, we must check for overflow or underflow—that is, we must make sure that the exponent still fits in its field.

Step 4. Since we assumed that the significand can be only four digits long (excluding the sign), we must round the number. In our grammar school algorithm, the rules truncate the number if the digit to the right of the desired point is between 0 and 4 and add 1 to the digit if the number to the right is between 5 and 9. The number

$$1.0015_{\rm mm} \times 10^2$$

is rounded to four digits in the significand to

$$1.002 \times 10^{2}$$

since the fourth digit to the right of the decimal point was between 5 and 9. Notice that if we have bad luck on rounding, such as adding 1 to a string of 9s, the sum may no longer be normalized and we would need to perform step 3 again.

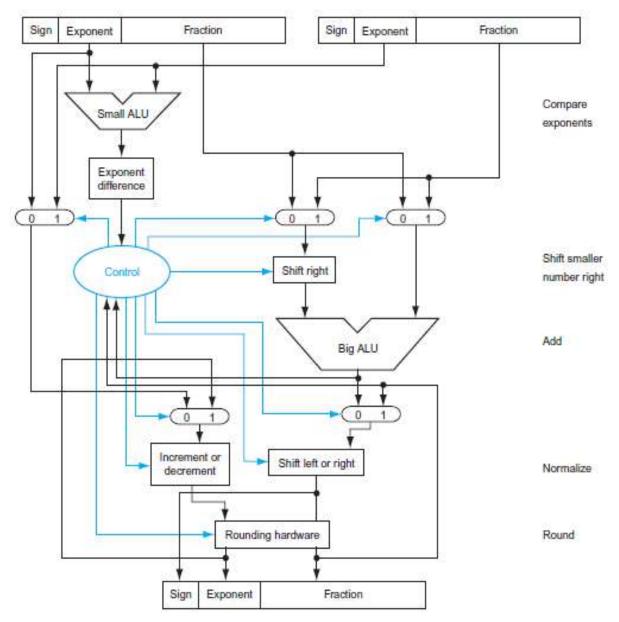

### **BLOCK DIAGRAM OF ARITHEMETIC UNIT TO FLOATING POINT ADDITION**

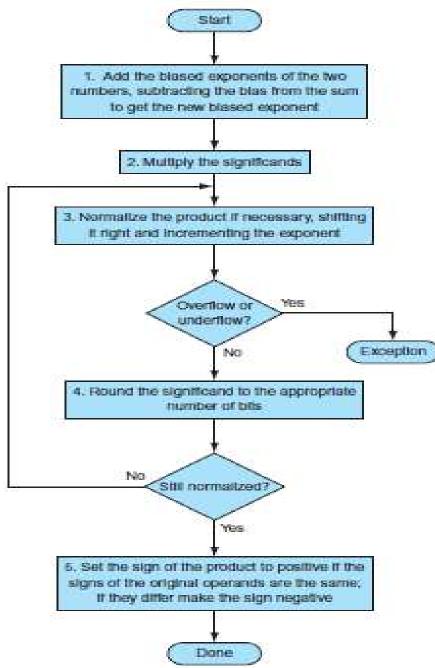

#### **FLOATING POINT MULTIPLICATION** FLOATING POINT MULTIPLICATION ALGORITHM

**Step1:** Add the biased exponent and subtract the bias (127 for Sp and 1023 for Dp).

**Step 2:** Multiply the significands.

Step3: Normalize the result if required shift right and incrementing the exponent and check for overflow / under flow.

Step4: Round the significand to appropriate number of bits and normalize if required.

**Step 5:** Set the sign of the product.

### **FLOWCHART**

#### EXAMPLE

#### **Binary Floating-Point Multiplication**

Let's try multiplying the numbers  $0.5_{ten}$  and  $-0.4375_{ten}$ , using the steps in Figure 3.16.

In binary, the task is multiplying  $1.000_{two} \times 2^{-1}$  by  $-1.110_{two} \times 2^{-2}$ .

Step 1. Adding the exponents without bias:

$$-1 + (-2) = -3$$

or, using the biased representation:

(-1 + 127) + (-2 + 127) - 127 = (-1 - 2) + (127 + 127 - 127)= -3 + 127 = 124

Step 2. Multiplying the significands:

$$\times \underbrace{\begin{array}{c} 1.000_{two} \\ 0.000 \\ 1000 \\ 1000 \\ 1000 \\ 1000 \\ 1110000_{two} \end{array}}_{two}$$

The product is  $1.110000_{two} \times 2^{-3}$ , but we need to keep it to 4 bits, so it is  $1.110_{two} \times 2^{-3}$ .

Step 3. Now we check the product to make sure it is normalized, and then check the exponent for overflow or underflow. The product is already normalized and, since 127 ≥ -3 ≥ -126, there is no overflow or underflow. (Using the biased representation, 254 ≥ 124 ≥ 1, so the exponent fits.)

Step 4. Rounding the product makes no change:

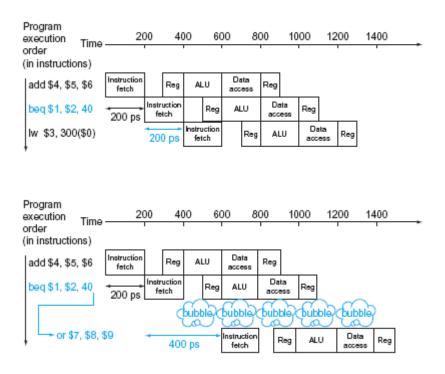

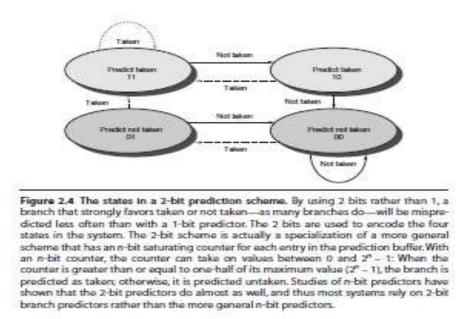

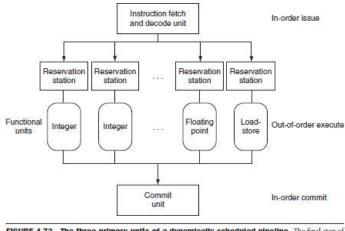

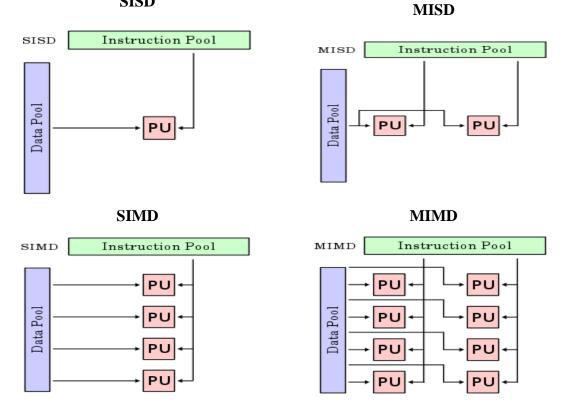

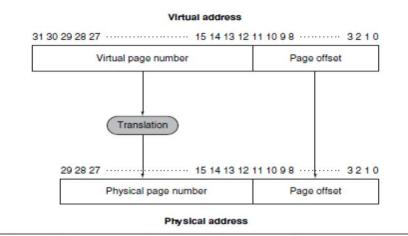

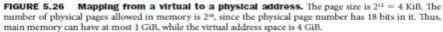

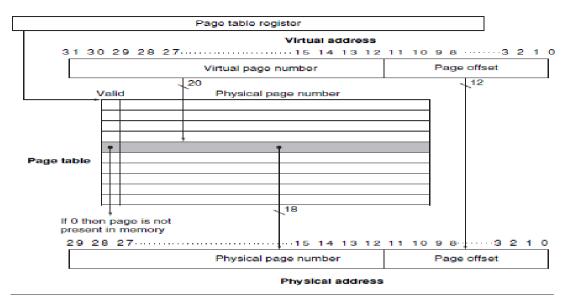

$$1.110_{two} \times 2^{-3}$$